15 double buffer control – Renesas SH7781 User Manual

Page 983

19. Display Unit (DU)

Rev.1.00 Jan. 10, 2008 Page 953 of 1658

REJ09B0261-0100

19.4.15

Double Buffer Control

The double buffer control of the display unit (DU) includes two types of functions, which are a

manual display change mode in which display switching is all controlled by software, and an auto

display change mode to realize blinking.

In the case of manual display change mode, the display change is performed in frame units for

non-interlaced and interlaced sync display, and in field units for interlaced sync & video display.

In the case of auto display change mode, all switching is performed in field units.

Manual Display Change Mode: In manual display change mode, display frame switching is

controlled by software. Display switching can either be performed by software using the PnDC bit

in PnMR, or by setting the buffer 0 or buffer 1 start address in PnDSA0R and PnDSA1R indicated

by the DFBn bit in DSSR.

When making a transition from this mode to another mode, the PnDC bit should always be set to 1

first.

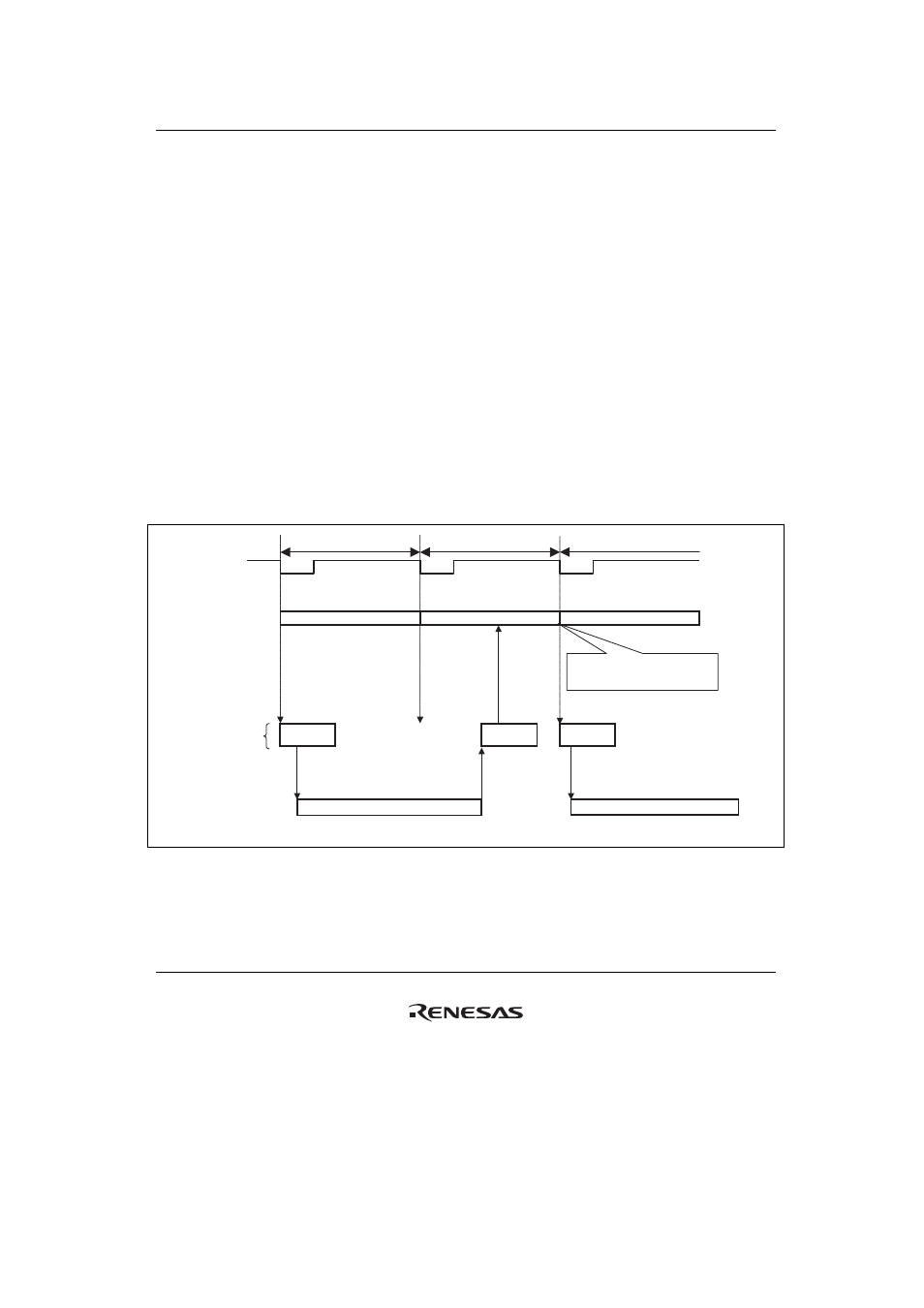

The following shows a control example for the manual display mode.

VSYNC

(Non-interlaced)

Display screen

operation

A0 display

A0 display

A1 display

First frame

Second frame

Third frame

Interrupt

processing

Interrupt

processing

Interrupt

processing

Start of

transfer

Start of

transfer

CPU operation

A0: Display area start address 0

A1: Display area start address 1

VBK: VBK bit in DSSR

Transfer of display data for A1

Transfer of display data for A0

Display is switched by

the PnDC bit or DSAR

at the falling edge of VSYNC.

Display data

transfer by a

VBK interrupt

If display data

transfer for B1 has

not been completed,

a VBK interrupt is

ignored.

PnDC bit is set to 1,

or

DSAR address is

set.

The PnDC bit is

set by a transfer

end interrupt.

Auto Display Change Mode: For information on the auto display change mode, refer to section

19.4.11, Blinking.