Renesas SH7781 User Manual

Page 306

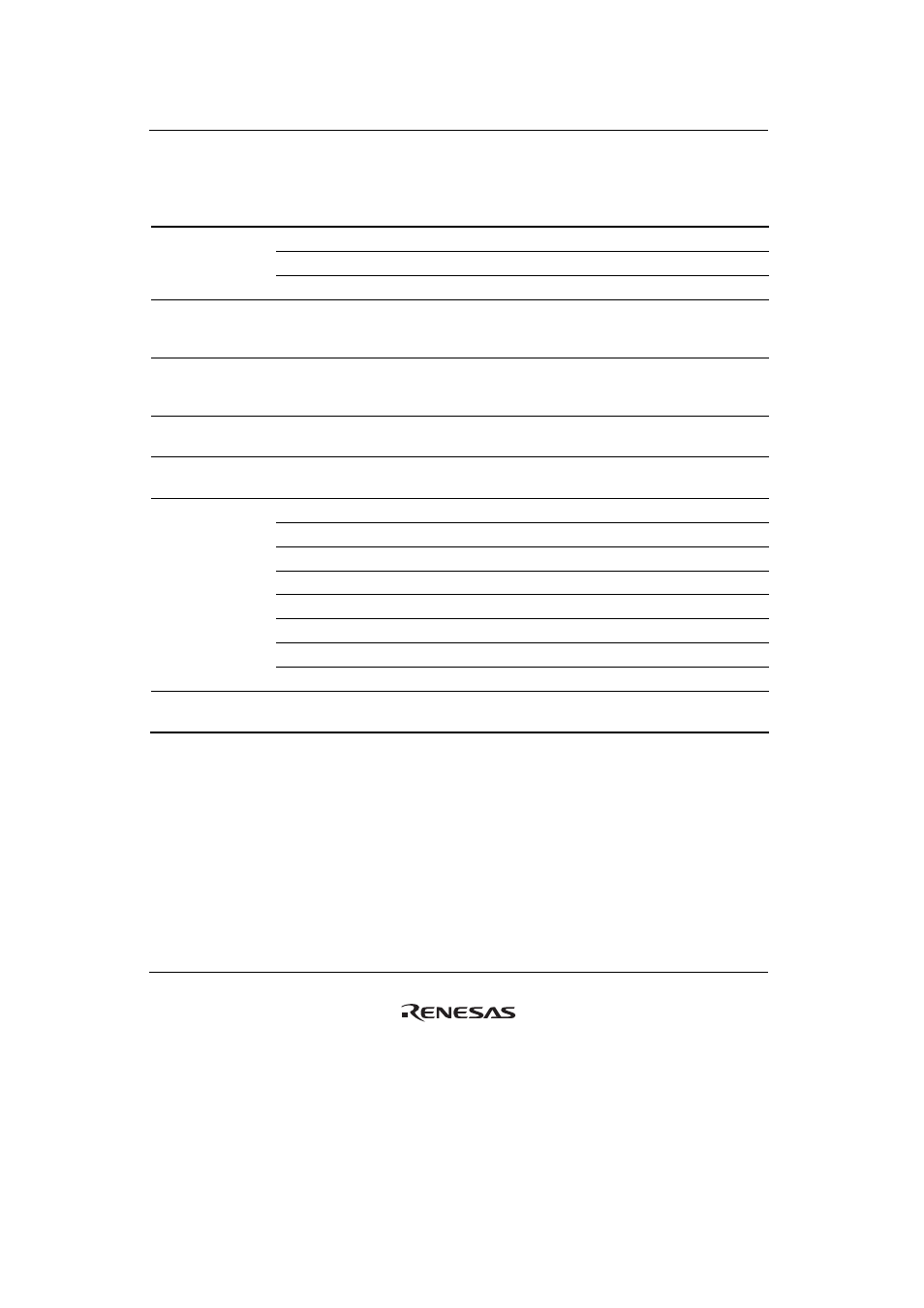

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 276 of 1658

REJ09B0261-0100

Name Abbreviation

Power-on

Reset by

PRESET

Pin/WDT/H-UDI

Manual Reset

by

WDT/Multiple

Exception

Sleep by

SLEEP

Instruction

Deep Sleep by

SLEEP

Instruction

(DSLP

= 1)

INT2PRI7

H'0000 0000

H'0000 0000

Retained

Retained

INT2PRI8

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt priority

registers

INT2PRI9

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt source

register (not affected

by the mask state)

INT2A0 H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

Interrupt source

register (affected by

the mask state)

INT2A1

H'0000 0000

H'0000 0000

Retained

Retained

Interrupt mask

register

INT2MSKR

H'FFFF FFFF

H'FFFF FFFF

Retained

Retained

Interrupt mask clear

register

INT2MSKCR

H'0000 0000

H'0000 0000

Retained

Retained

INT2B0 H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B1 H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

Module interrupt

source registers

INT2B2 H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B3

H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B4

H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B5

H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B6

H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

INT2B7

H'xxxx

xxxx

H'xxxx xxxx

Retained

Retained

GPIO interrupt set

register

INT2GPIC

H'0000 0000

H'0000 0000

Retained

Retained

Note: * initial values of ICR0.NMIL and NMIFCR.NMIL depend on the level input to the NMI pin.