Renesas SH7781 User Manual

Page 363

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 333 of 1658

REJ09B0261-0100

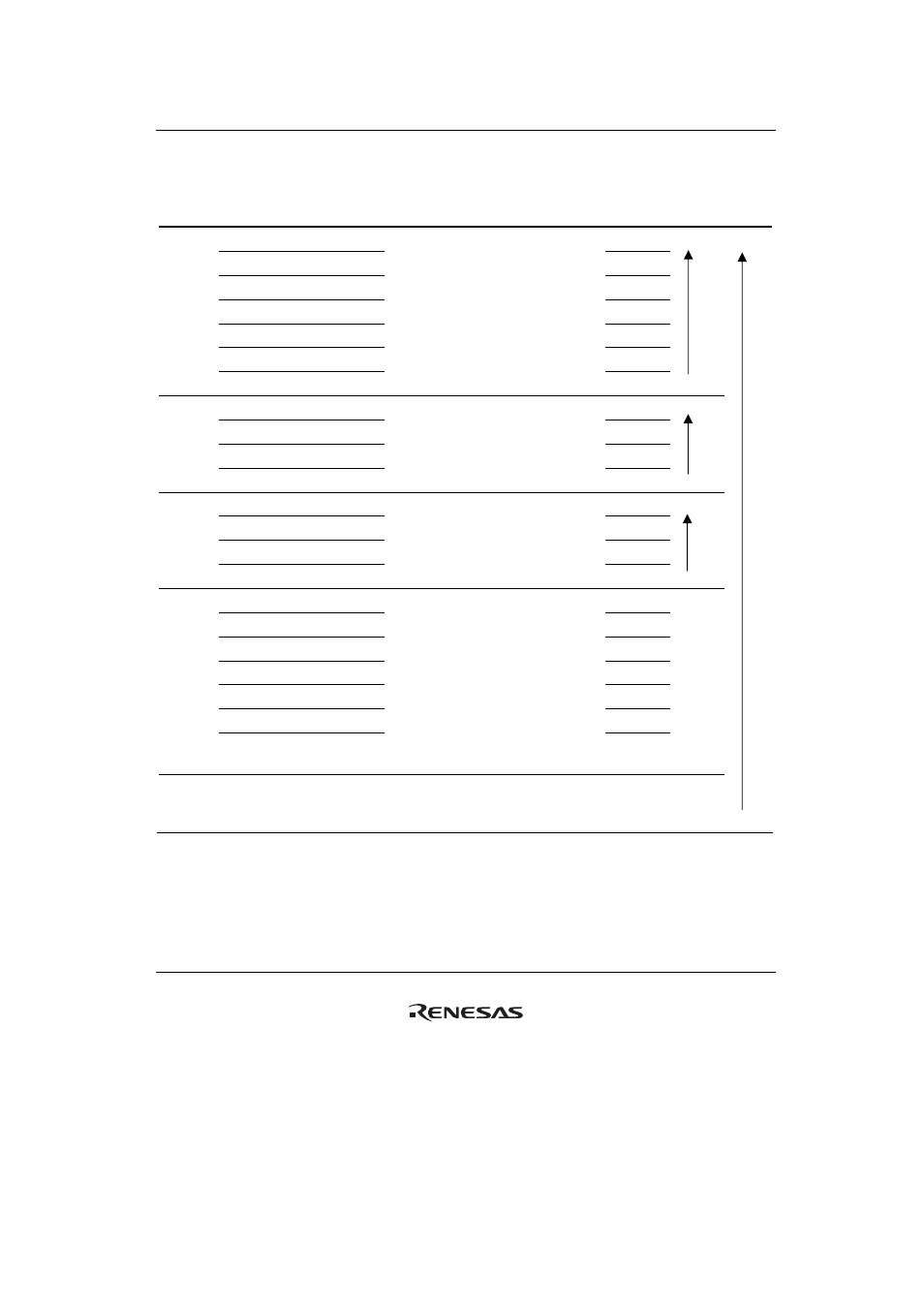

Interrupt Source

INTEVT

Code

Interrupt

Priority

Mask/Clear

Register & Bit

Interrupt

Source

Register

Detail

Source

Register

Priority

within

Sets of

Sources

Default

Priority

DMAC(0) DMINT0* H'620

INT2B3[0]

High

High

DMINT1* H'640

INT2B3[1]

DMINT2* H'660

INT2PRI4

[20:16]

INT2MSKR[10]

INT2MSKCLR

[10]

INT2A0[10]

INT2A1[10]

INT2B3[2]

DMINT3* H'680

INT2B3[3]

DMINT4* H'6A0

INT2B3[4]

DMINT5* H'6C0

INT2B3[5]

DMAE (ch0 to ch5)* H'6E0

INT2B3[6] Low

SCIF-ch0 ERI0* H'700

INT2B2[0]

High

RXI0* H'720

INT2PRI2

[28:24]

INT2MSKR[2]

INT2MSKCLR[2]

INT2A0[2]

INT2A1[2]

INT2B2[1]

BRI0* H'740

INT2B2[2]

TXI0* H'760

INT2B2[3]

Low

SCIF-ch1 ERI1* H'780

INT2B3[4]

High

RXI1* H'7A0

INT2PRI2

[20:16]

INT2MSKR[3]

INT2MSKCLR[3]

INT2A0[3]

INT2A1[3]

INT2B3[5]

BRI1* H'7C0

INT2B3[6]

TXI1* H'7E0

INT2B3[7] Low

DMAC(1) DMINT6* H'880

INT2B2[7]

DMINT7* H'8A0

INT2B2[8]

DMINT8* H'8C0

INT2PRI4

[12:8]

INT2MSKR[11]

INT2MSKCLR

[11]

INT2A0[11]

INT2A1[11]

INT2B2[9]

DMINT9* H'8E0

INT2B2[10]

DMINT10* H'900

INT2B3[11]

DMINT11* H'920

INT2B3[12]

DMAE

(ch6

to

ch11)*

H'940

INT2B3[13]

HSPI SPII

H'960

INT2PRI7

[20:16]

INT2MSKR[21]

INT2MSKCLR

[21]

INT2A0[21]

INT2A1[21]

⎯

Low