14 sdram mode setting register (dbmrcnt) – Renesas SH7781 User Manual

Page 540

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 510 of 1658

REJ09B0261-0100

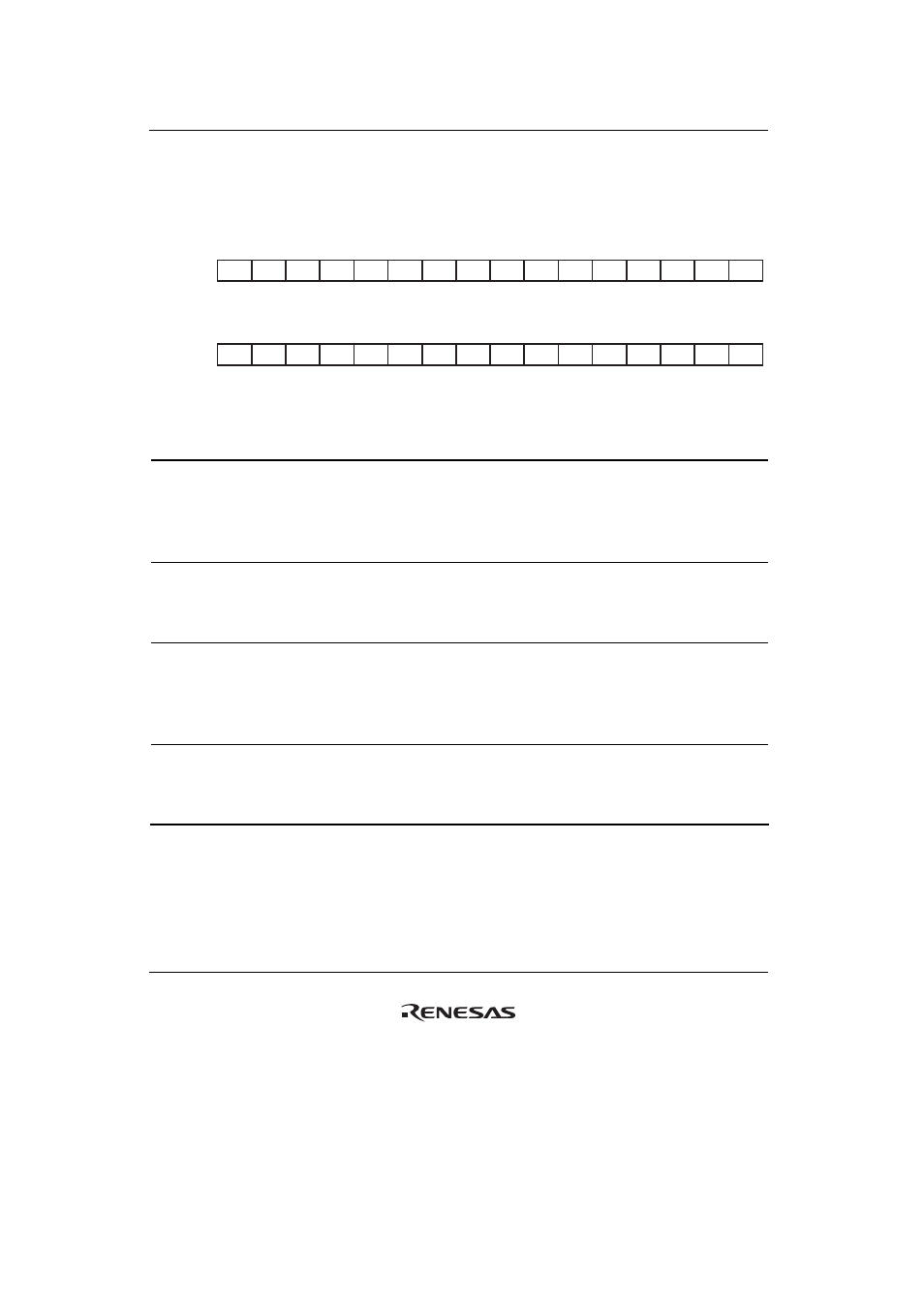

12.4.14

SDRAM Mode Setting Register (DBMRCNT)

The SDRAM mode setting register (DBMRCNT) is a write-only register. If it is read, correct

operation cannot be guaranteed.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

BA0

BA1

BA2

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

⎯

MA14

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 19

⎯

Undefined W

Reserved

These bits are always read as 0. The write value should

always be 0.

If a value other than 0 is written, correct operation

cannot be guaranteed.

18 to 16 BA2 to BA0 Undefined W

SDRAM Mode Register and Extended Mode Register

Setting Bits

Bank address pins MBA2, MBA1, and MBA0

correspond to bit 18, bit 17, and bit 16, respectively.

15

⎯

Undefined W

Reserved

This bit is always read as 0. The write value should

always be 0.

If a value other than 0 is written, correct operation

cannot be guaranteed.

14 to 0

MA14 to

MA0

Undefined W

SDRAM Mode Register and Extended Mode Register

Setting Bits

The address pins MA14, MA13, ..., and MA0

correspond to bit 14, bit 13, ..., and bit 0, respectively.