2 exception source acceptance – Renesas SH7781 User Manual

Page 130

5. Exception Handling

Rev.1.00 Jan. 10, 2008 Page 100 of 1658

REJ09B0261-0100

5.5.2

Exception Source Acceptance

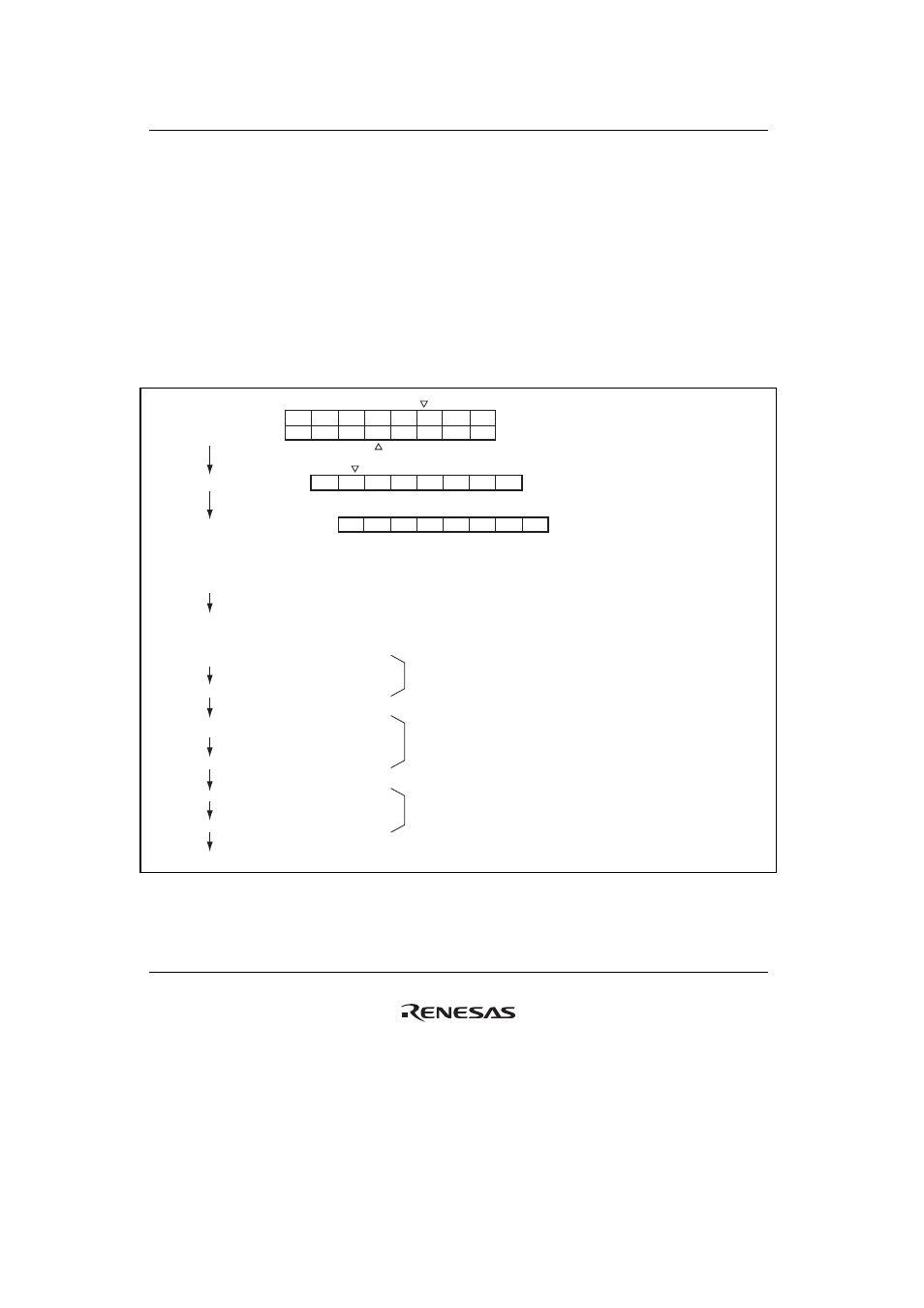

A priority ranking is provided for all exceptions for use in determining which of two or more

simultaneously generated exceptions should be accepted. Five of the general exceptions—general

illegal instruction exception, slot illegal instruction exception, general FPU disable exception, slot

FPU disable exception, and unconditional trap exception—are detected in the process of

instruction decoding, and do not occur simultaneously in the instruction pipeline. These

exceptions therefore all have the same priority. General exceptions are detected in the order of

instruction execution. However, exception handling is performed in the order of instruction flow

(program order). Thus, an exception for an earlier instruction is accepted before that for a later

instruction. An example of the order of acceptance for general exceptions is shown in figure 5.2.

I1

I1

ID

ID

E3

WB

WB

TLB miss (data access)

Pipeline flow:

Order of detection:

Instruction n

Instruction n + 1

General illegal instruction exception (instruction n + 1) and

TLB miss (instruction n + 2) are detected simultaneously

Order of exception handling:

TLB miss (instruction n)

Program order

1

Instruction n + 2

General illegal instruction exception

I1

ID

WB

WB

TLB miss (instruction access)

2

3

4

I1, I2, I3:

Instruction fetch

ID :

Instruction decode

E1, E2, E3: Instruction execution

(E2, E3 Memory access)

WB Write-back

Instruction n + 3

TLB miss (instruction n)

Re-execution of instruction n

General illegal instruction exception

(instruction n + 1)

Re-execution of instruction n + 1

TLB miss (instruction n + 2)

Re-execution of instruction n + 2

Execution of instruction n + 3

Legend:

E3

E3

E2

E2

E1

E1

I2

I2

I3

I3

E1

E1

E2

E2

E3

I2

I3

I3

ID

I2

I1

Figure 5.2 Example of General Exception Acceptance Order