10 sdram refresh control register 2 (dbrfcnt2) – Renesas SH7781 User Manual

Page 532

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 502 of 1658

REJ09B0261-0100

12.4.10

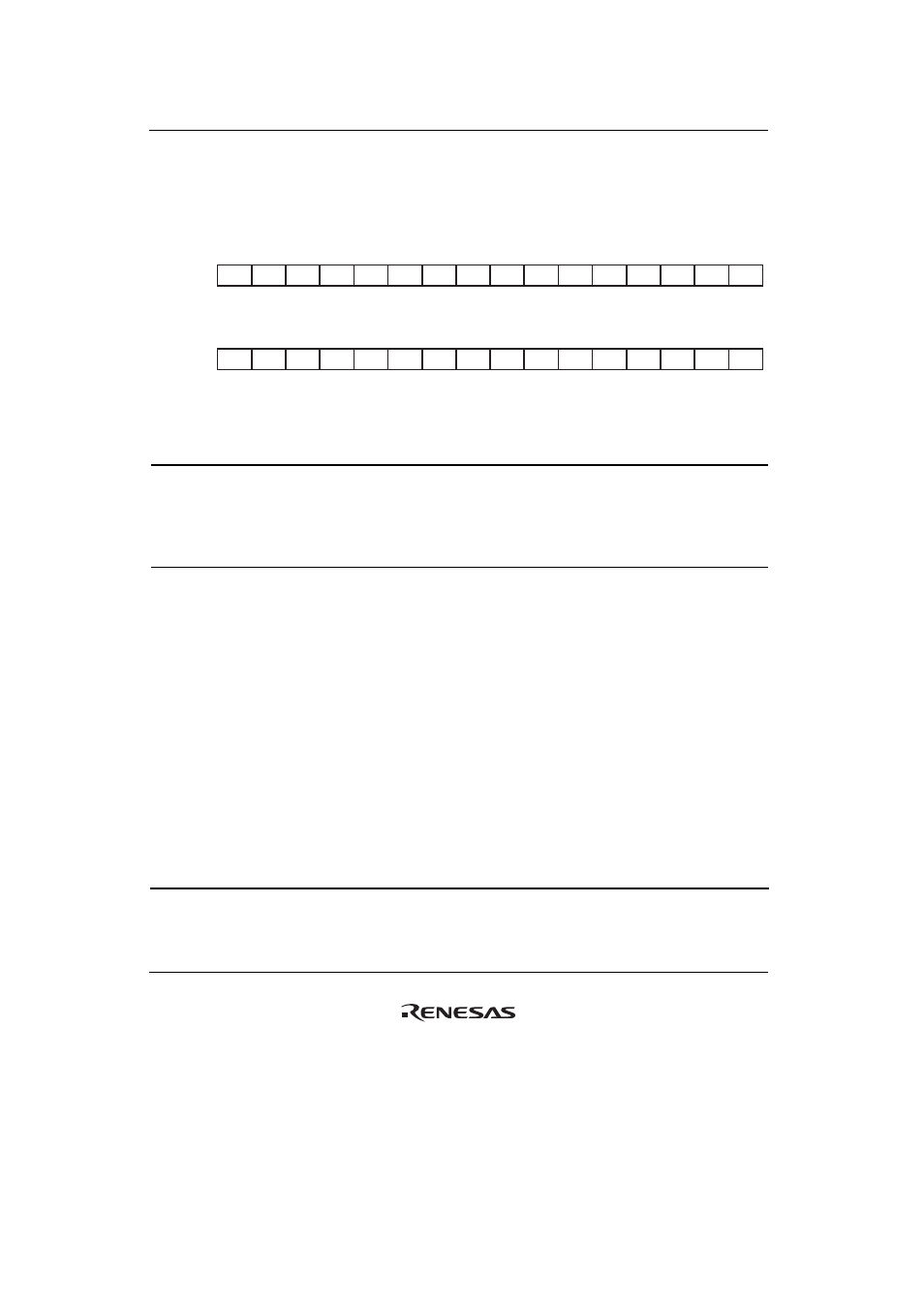

SDRAM Refresh Control Register 2 (DBRFCNT2)

The SDRAM refresh control register 2 (DBRFCNT2) is a readable/writable register. It is

initialized only upon power-on reset.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

LV1

TH0

LV1

TH1

LV1

TH2

LV1

TH3

LV1

TH4

LV1

TH5

LV1

TH6

LV1

TH7

LV1

TH8

LV1

TH9

LV1

TH10

LV1

TH11

LV1

TH12

LV1

TH13

⎯

LV1

TH14

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R/W

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

LV0

TH0

LV0

TH1

LV0

TH2

LV0

TH3

LV0

TH4

LV0

TH5

LV0

TH6

LV0

TH7

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31

⎯

0 R

Reserved

This bit is always read as 0. The write value should

always be 0.

Operation when a value other than 0 is written is not

guaranteed.

30 to 16 LV1TH14 to

LV1TH0

001 0000

0000 0000

R/W

Level 1 Threshold Setting Bits

These bits set the threshold cycles for executing auto-

refresh when there is a vacancy in access requests

received via the SuperHyway bus.

The number of cycles is the number of DDR clock

cycles.

When the internal refresh counter value exceeds

LV1TH, and there are consecutive requests received via

the SuperHyway bus, request processing is given

priority over auto-refresh.

The relation between LV1TH and LV0TH must satisfy

the relation LV1TH

≥ LV0TH. Correct operation cannot

be guaranteed if LV1TH <LV0TH.

The value of LV1TH should be set larger than the

constraint TRAS between PRE and ACT set in the

SDRAM timing register 0. If a value equal to or less than

TRAS is set, Correct operation cannot be guaranteed.