3 watchdog timer base stop time register (wdtbst) – Renesas SH7781 User Manual

Page 796

16. Watchdog Timer and Reset (WDT)

Rev.1.00 Jan. 10, 2008 Page 766 of 1658

REJ09B0261-0100

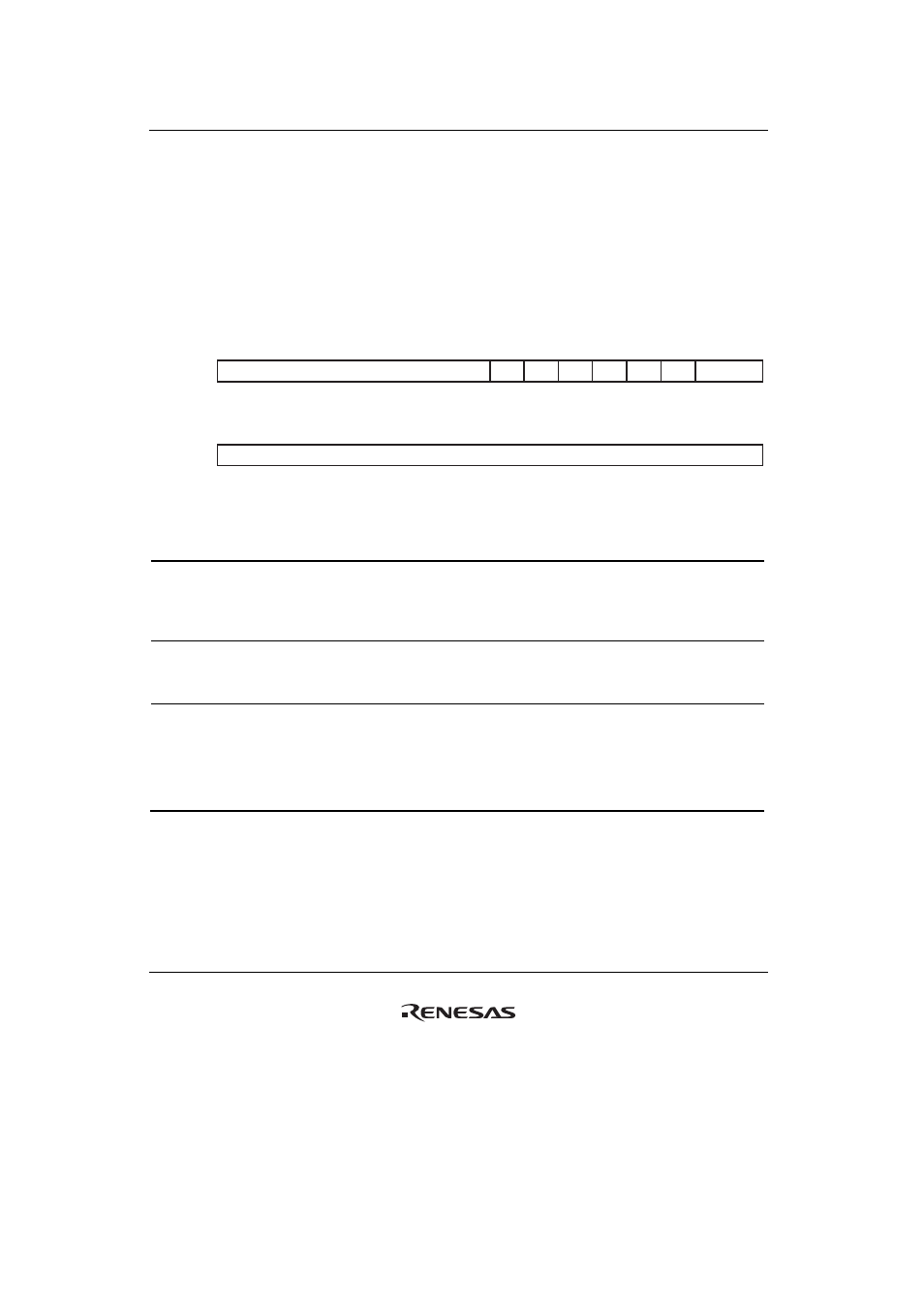

16.3.3

Watchdog Timer Base Stop Time Register (WDTBST)

WDTBST is a 32-bit readable/writable register that specifies the time until counter WDTBCNT

overflows when the bus clock frequency has been changed. The time until WDTBCNT overflows

becomes minimum when H'5500 0001 is set, and maximum when H'5500 0000 is set.

WDTBST should be written to as a longword unit, with H'55 in the most significant byte. The

value read from this byte is always H'00. WDTBST is only rest by a power-on reset caused by the

PRESET pin.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

WDTBST

⎯

⎯

⎯

⎯

R/W

R/W

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

WDTBST

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

Code for writing (H'55)

⎯

⎯

Bit Bit

Name

Initial

Value R/W Description

31 to 24 (Code for

writing)

All 0

R/W

Code for writing (H'55)

These bits are always read as H'00. When writing to

this register, the value written to these bits must be

H'55.

23 to 18

⎯ All

0

R

Reserved

These bits are always read as 0. The write value

should always be 0.

17 to 0

WDTBST

All 0

R/W

Base Timer Stop

These bits set the counter value at which WDTBCNT

overflows.

H'00001: Minimum overflow value

H'00000: Maximum overflow value