10 ddr2-sdram power supply backup function – Renesas SH7781 User Manual

Page 576

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 546 of 1658

REJ09B0261-0100

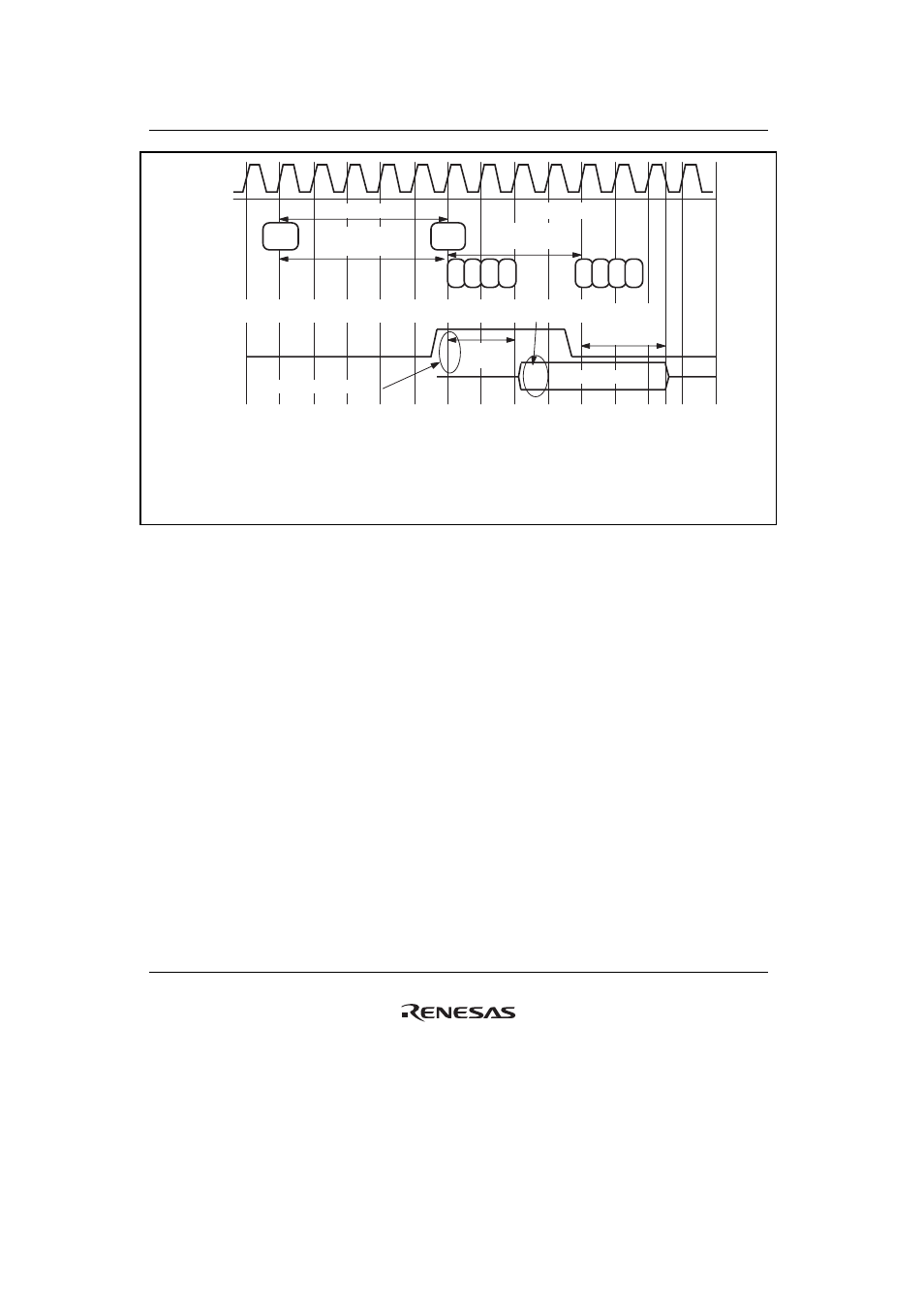

write

MCK

Command

Data

MCKE

MODT

Terminating

resistor

in SDRAM

read

The above figure shows an example when a product with CL = 5 is used. As the ODT control signal (MODT)

is extended for one cycle, the product with CL = 5 or greater is required. If a product with CL = 4 or less is

used, MODT needs to be asserted before the issue of the WRITE command, which is not supported by this

LSI.

The interval between the READ and WRITE commands required for the SDRAM is assumed to be 4 cycles.

However, if the interval is 4 cycles, read data exists on the data bus when the terminating resistor in the

SDRAM is turned on since MODT is extended for one cycle. To prevent this, the interval should be set to 5

cycles.

5 cycles for

product with CL = 5

4 -> 5 cycles

tAOND

= 2 cycles

Extended for 1 cycle

tAOFD

= 2.5 cycles

If the interval from the READ command to the WRITE command is 4 cycles, read data exists

on the data bus when Rtt is turned on. Therefore, the interval should be 5 cycles.

Resistor ON

4 cycles for

product with CL = 5

High level

Figure 12.22 Important Information on One-Cycle Extension of ODT Control Signal

12.5.10

DDR2-SDRAM Power Supply Backup Function

The SDRAM power supply backup function utilizes the SDRAM self-refresh state to turn off the

power supply to most of the modules including the DBSC2 (all modules except the 1.8 V I/O),

while maintaining the data in the SDRAM. By using this function, not only is it possible to cut

power consumption, but the time needed to transfer data once again to the SDRAM can be

eliminated, since the valid data is maintained within the SDRAM (see figure 12.23). In order to

realize this function, in addition to the LSI device containing the DBSC2, a separate external

control circuit (microcomputer or similar) is needed to monitor the states of this LSI and the

memory.