Renesas SH7781 User Manual

Page 511

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 481 of 1658

REJ09B0261-0100

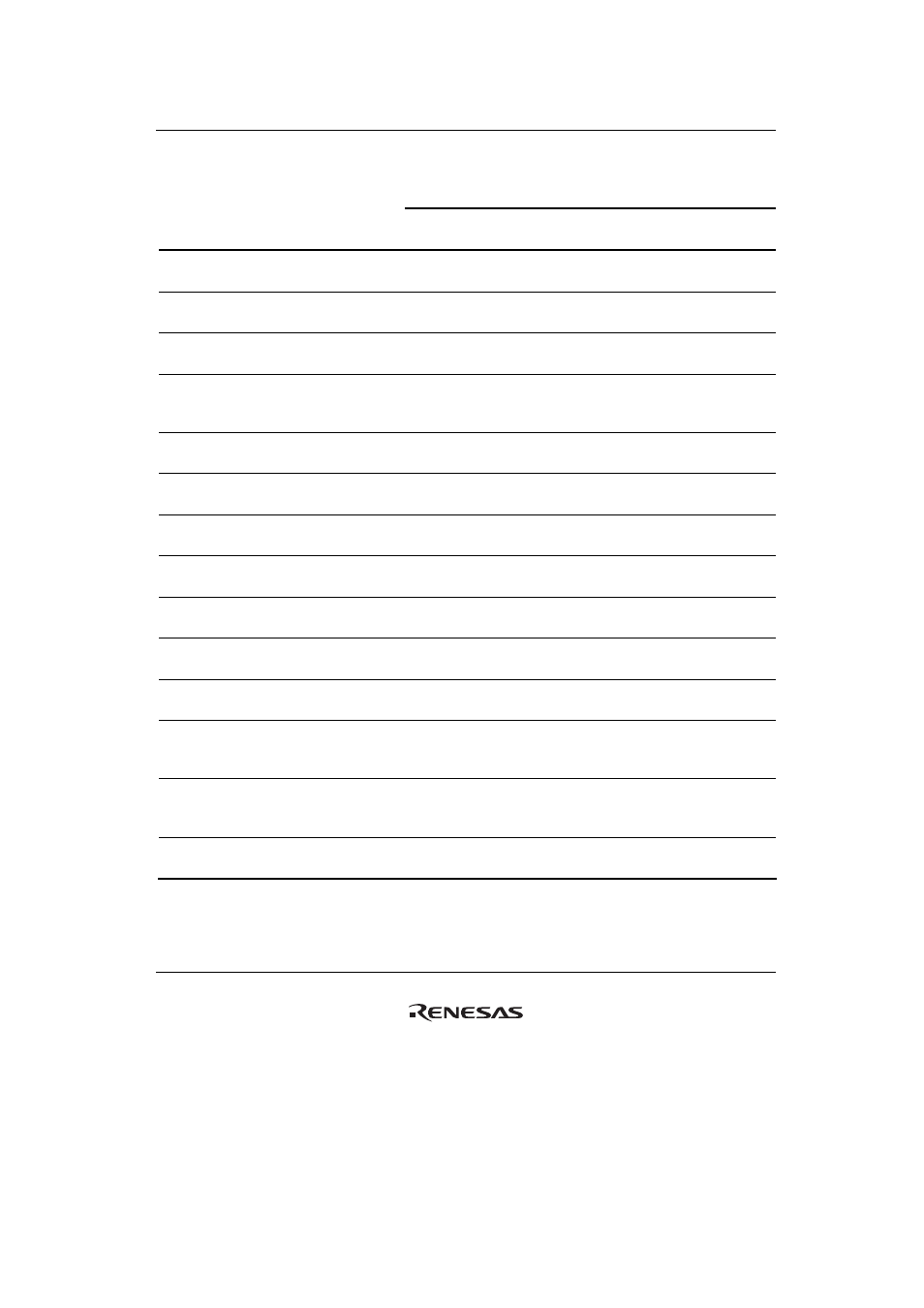

Table 12.10 Register Status in each Processing Mode

Power-On Reset Manual Reset

Sleep/Deep Sleep

Register Name

Abbreviation

By

PRESET pin/

WDT/H-UDI

By WDT/Multiple

Exception

By SLEEP

Instruction

DBSC2 status

register

DBSTATE H'0000

0x00* Retained

Retained

SDRAM operation

enable register

DBEN H'0000

0000

Retained

Retained

SDRAM command

control register

DBCMDCNT H'0000

0000 Retained

Retained

SDRAM

configuration

setting register

DBCONF H'009A

0001

Retained Retained

SDRAM timing

register 0

DBTR0 H'0203

0501

Retained

Retained

SDRAM timing

register 1

DBTR1 H'0001

0001

Retained

Retained

SDRAM timing

register 2

DBTR2 H'0104

0303

Retained

Retained

SDRAM refresh

control register 0

DBRFCNT0 H'0000

0000 Retained

Retained

SDRAM refresh

control register 1

DBRFCNT1 H'0000

0200 Retained

Retained

SDRAM refresh

control register 2

DBRFCNT2 H'1000

0080 Retained

Retained

SDRAM refresh

status register

DBRFSTS H'0000

0000

Retained Retained

DDRPAD

frequency setting

register

DBFREQ H'0000

0000

Retained Retained

DDRPAD DIC,

ODT, OCD setting

register

DBDICODTOCD H'0000

0007

Retained

Retained

SDRAM mode

setting register

DBMRCNT Undefined Retained

Retained

Note: * Initial value is specified by external pin MODE8.