3 register descriptions – Renesas SH7781 User Manual

Page 1372

27. NAND Flash Memory Controller (FLCTL)

Rev.1.00 Jan. 10, 2008 Page 1342 of 1658

REJ09B0261-0100

27.3

Register Descriptions

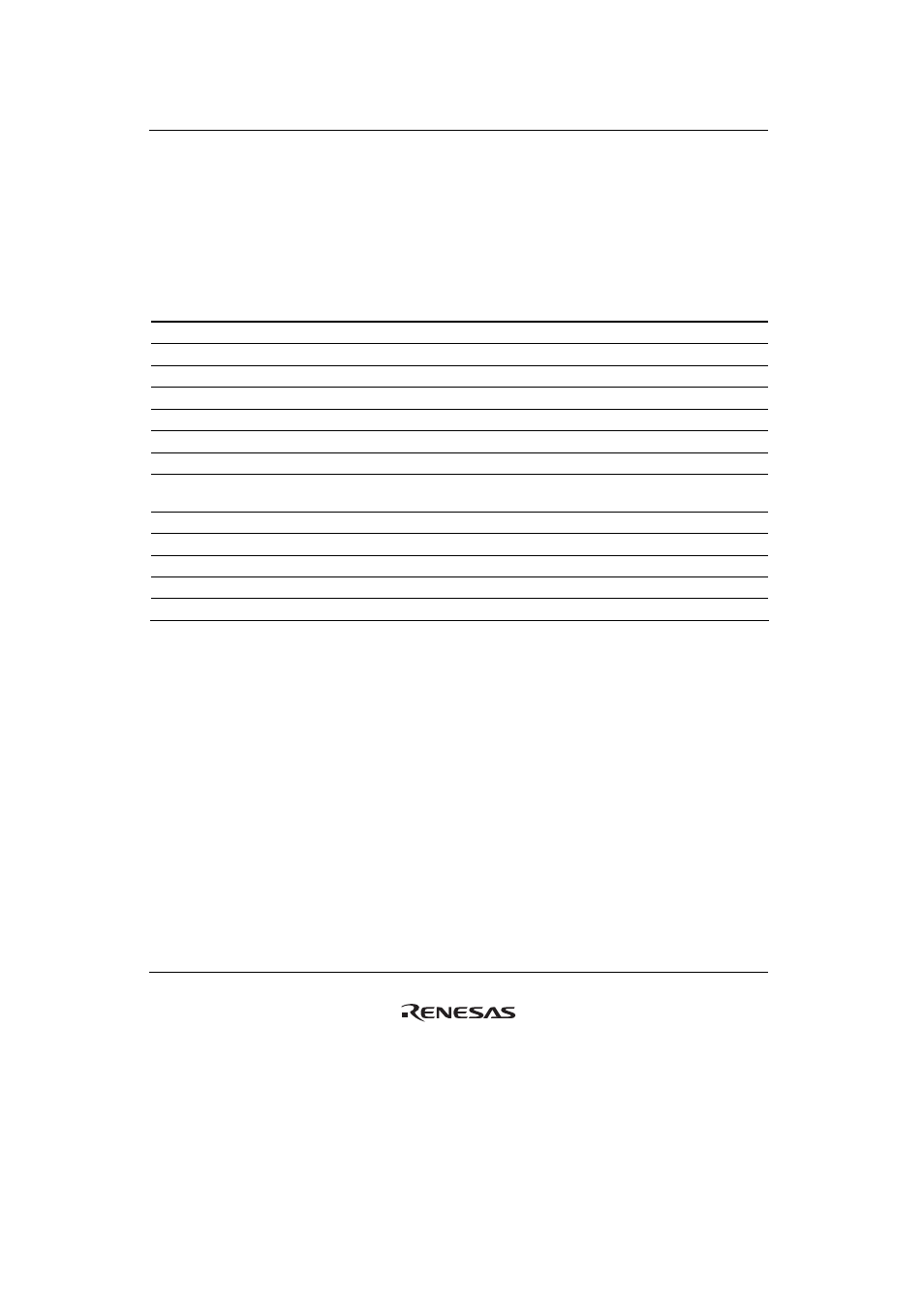

Table 27.2 shows the register configuration of FLCTL. Table 27.3 shows the register states in

each processing mode.

Table 27.2 Register Configuration of FLCTL

Register Name

Abbreviation

R/W P4 Address

Area 7 Address

Access

Size

Sync

Clock

Common control register

FLCMNCR

R/W H'FFE9 0000

H'1FE9 0000

32

Pck

Command control register

FLCMDCR

R/W H'FFE9 0004

H'1FE9 0004

32

Pck

Command code register

FLCMCDR

R/W H'FFE9 0008

H'1FE9 0008

32

Pck

Address register

FLADR

R/W H'FFE9 000C

H'1FE9 000C

32

Pck

Data register

FLDATAR

R/W H'FFE9 0010

H'1FE9 0010

32

Pck

Data counter register

FLDTCNTR

R/W H'FFE9 0014

H'1FE9 0014

32

Pck

Interrupt DMA control register FLINTDMACR R/W H'FFE9 0018

H'1FE9 0018

32

Pck

Ready busy timeout setting

register

FLBSYTMR R/W

H'FFE9

001C H'1FE9

001C 32

Pck

Ready busy timeout counter

FLBSYCNT

R

H'FFE9 0020

H'1FE9 0020

32

Pck

Data FIFO register

FLDTFIFO

R/W H'FFE9 0024

H'1FE9 0024

32

Pck

Control code FIFO register

FLECFIFO

R/W H'FFE9 0028

H'1FE9 0028

32

Pck

Transfer control register

FLTRCR

R/W H'FFE9 002C

H'1FE9 002C

8

Pck

Address register 2

FLADR2

R/W H'FFE9 003C

H'1FE9 003C

32

Pck