Renesas SH7781 User Manual

Page 356

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 326 of 1658

REJ09B0261-0100

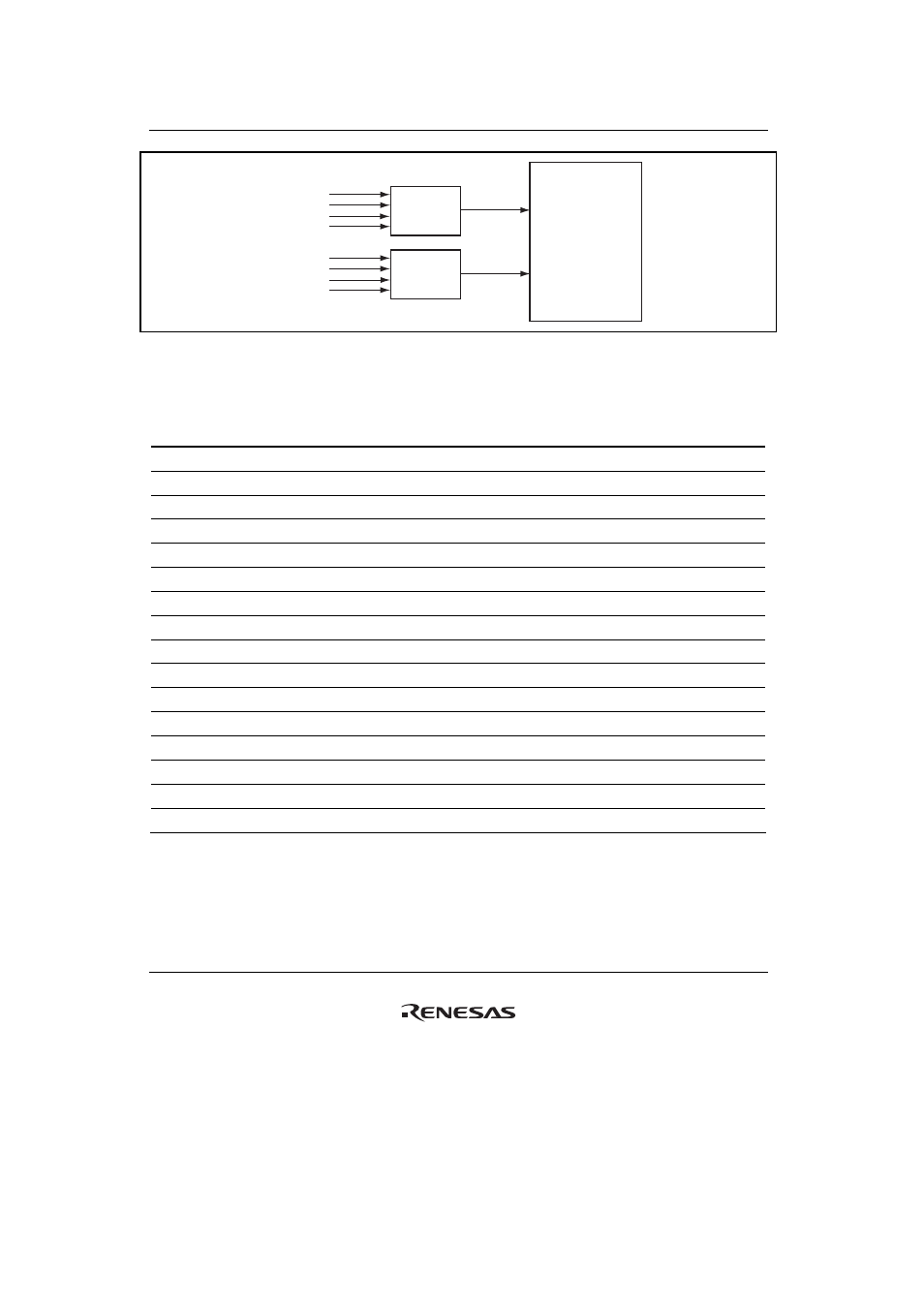

Priority

encoder

Interrupt

requests

SH7785

IRQ/

IRL3 to

IRQ/

IRL0

IRQ/

IRL7 to

IRQ/

IRL4

IRL7 to IRL4

IRL3 to IRL0

Interrupt

requests

Priority

encoder

Figure 10.3 Example of IRL Interrupt Connection

Table 10.12 IRL Interrupt Pins (IRL[3:0], IRL[7:4]) and Interrupt Levels

IRL3 or

IRL7

IRL2 or

IRL6

IRL1 or

IRL5

IRL0 or

IRL4

Interrupt

Priority Level

Interrupt Request

Low Low Low Low 15

Level

15

interrupt

request

Low Low Low High 14

Level

14

interrupt

request

Low Low High Low 13

Level

13

interrupt

request

Low Low High High 12

Level

12

interrupt

request

Low High Low Low 11

Level

11

interrupt

request

Low High Low High 10

Level

10

interrupt

request

Low High High Low 9

Level

9

interrupt

request

Low High High High 8

Level

8

interrupt

request

High Low Low Low 7

Level

7

interrupt

request

High Low Low High 6

Level

6

interrupt

request

High Low High Low 5

Level

5

interrupt

request

High Low High High 4

Level

4

interrupt

request

High High Low Low 3

Level

3

interrupt

request

High High Low High 2

Level

2

interrupt

request

High High High Low 1

Level

1

interrupt

request

High High High High 0

No

interrupt

request

IRL interrupt detection requires an on-chip noise-cancellation feature. This detection is performed

when the level sampled at every bus clock is the same for three consecutive cycles. This detection

can prevent the incorrect level from being taking in when the IRL interrupt pin state changes.