Renesas SH7781 User Manual

Page 1671

Appendix

Rev.1.00 Jan. 10, 2008 Page 1641 of 1658

REJ09B0261-0100

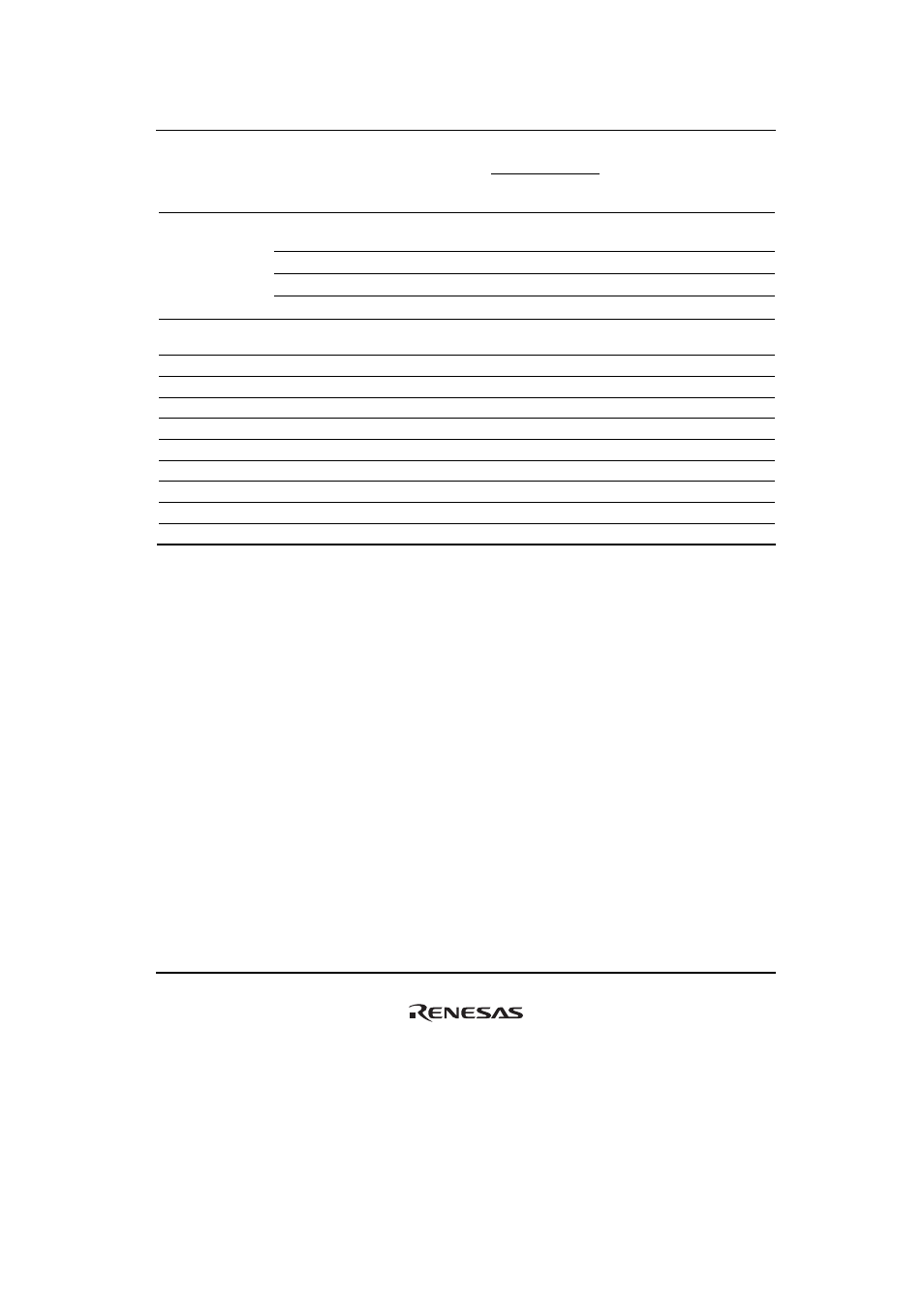

Reset

Pin Name

(LSI level)

Pin Name

(Module level)

Related

Module I/O

Power

-on

Manual Sleep

Module

Standby

Bus

Release

Port N6

(default)

GPIO I/O

PI K

K

⎯

K

SCIF5_SCK SCIF I/O

⎯

I K

K K

HAC1_SDOUT HAC

O

⎯

O O O O

SCIF5_SCK/

HAC1_SDOUT/

SSI1_SDATA

SSI1_SDATA SSI

I/O

⎯

I K

K K

ASEBRK/

BRKACK

ASEBRK/

BRKACK

H-UDI I/O PI PI/O PI/O

⎯ PI/O

TCK TCK

H-UDI

I

PI

PI

PI

PI

PI

TRST

TRST H-UDI

I

PI

PI

PI

PI

PI

TDI TDI

H-UDI

I

PI

PI

PI

PI

PI

TMS TMS

H-UDI

I

PI

PI

PI

PI

PI

TDO TDO

H-UDI

O

O

O

O

O

O

AUDCK AUDCK

H-UDI

O

O

O

O

⎯ O

AUDSYNC AUDSYNC

H-UDI

O

O

O O

⎯ O

AUDATA[3:0] AUDATA[3:0]

H-UDI O O O O

⎯ O

MPMD MPMD

H-UDI

I

I

I

I

⎯ I

Legend:

⎯:

Disabled (not selected) or not supported

(m): LBSC

master

mode

(s):

LBSC slave mode

I: Input

O: Output

H: High

level

output

L:

Low level output

Z:

High impedance state

PI:

Input and pulled up with a built-in pull-up resistance.

PZ:

High impedance and pulled up with a built-in pull-up resistance.

K:

Retain the previous pin state.

POR: Power-on

reset

Notes: 1. Depends on the MODE9 pin setting.

2. After power-or reset, this pin is output state. Must not input signals immediately after

power-on reset.

3. Depends on the settings of the MODE[12:11] pin and corresponding registers.

4. When the bus mode selected by MODE11/MODE12 pins is PCI host bus bridge or

PCIC normal (non-host), clock must be input to PCICLK pin. When the bus mode

selected by MODE11/MODE12 pins is local bus or display unit, PCICLK pin must be

pulled-up to VDDQ or pulled-down to GND.