Renesas SH7781 User Manual

Page 1545

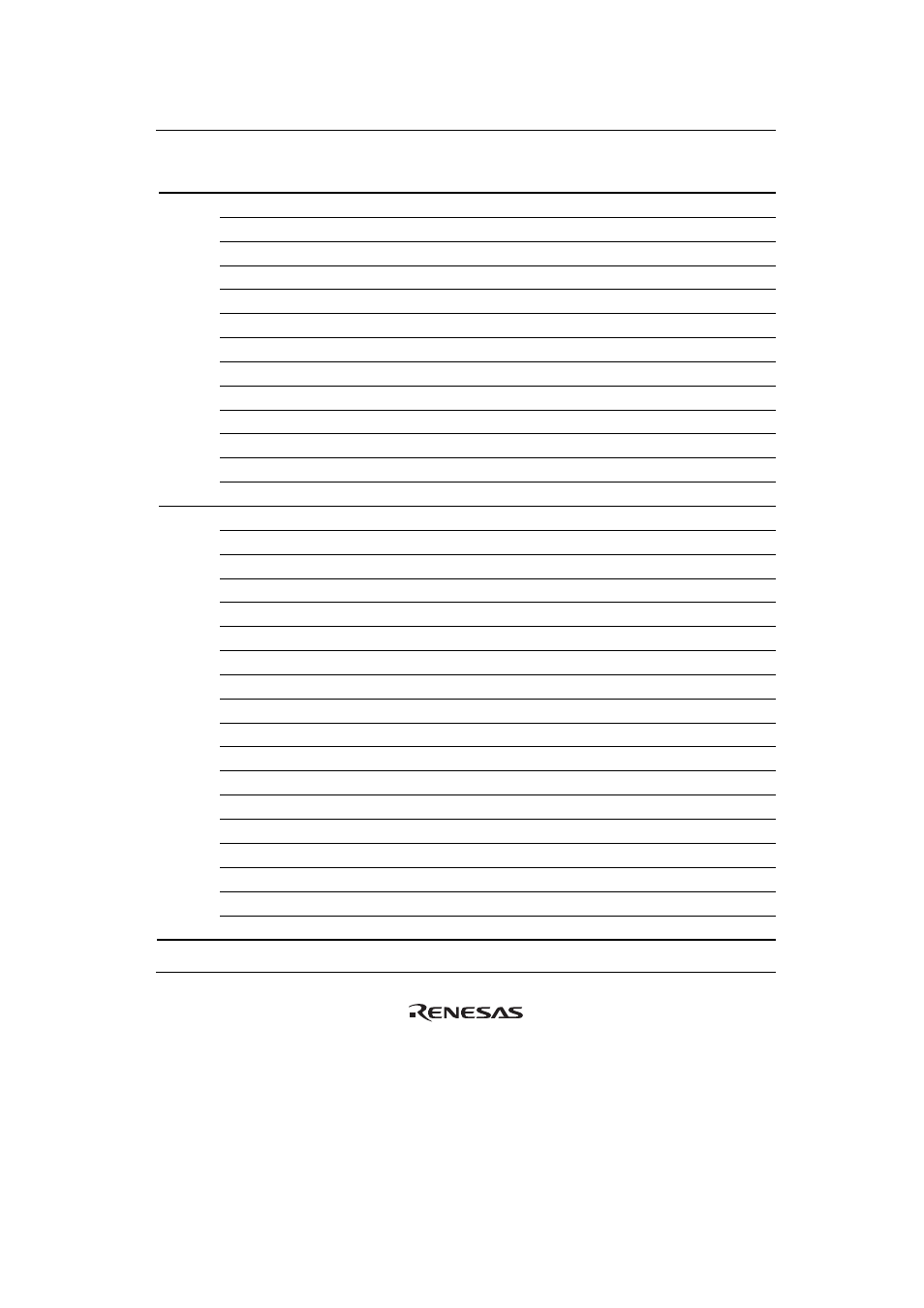

31. Register List

Rev.1.00 Jan. 10, 2008 Page 1515 of 1658

REJ09B0261-0100

Module

Name Name

Abbreviation

R/W

P4 Area

Address

Area 7

Address

Access

Size

PCIC

PCI memory bank register 0

PCIMBR0

R/W

H'FE04 01E0

H'1E04 01E0

32/16/8

PCI memory bank mask register 0

PCIMBMR0

R/W

H'FE04 01E4

H'1E04 01E4

32/16/8

PCI memory bank register 1

PCIMBR1

R/W

H'FE04 01E8

H'1E04 01E8

32/16/8

PCI memory bank mask register 1

PCIMBMR1

R/W

H'FE04 01EC H'1E04 01EC 32/16/8

PCI memory bank register 2

PCIMBR2

R/W

H'FE04 01F0

H'1E04 01F0

32/16/8

PCI memory bank mask register 2

PCIMBMR2

R/W

H'FE04 01F4

H'1E04 01F4

32/16/8

PCI I/O bank register

PCIIOBR

R/W

H'FE04 01F8

H'1E04 01F8

32/16/8

PCI I/O bank master register

PCIIOBMR

R/W

H'FE04 01FC H'1E04 01FC 32/16/8

PCI cache snoop control register 0

PCICSCR0

R/W

H'FE04 0210

H'1E04 0210

32/16/8

PCI cache snoop control register 1

PCICSCR1

R/W

H'FE04 0214

H'1E04 0214

32/16/8

PCI cache snoop address register 0

PCICSAR0

R/W

H'FE04 0218

H'1E04 0218

32/16/8

PCI cache snoop address register 1

PCICSAR1

R/W

H'FE04 021C H'1E04 021C

32/16/8

PCI PIO data register

PCIPDR

R/W

H'FE04 0220

H'1E04 0220

32/16/8

DMAC

DMA source address register 0 SAR0

R/W

H'FC80

8020

H'1C80

8020

32

DMA destination address register 0

DAR0

R/W

H'FC80 8024

H'1C80 8024

32

DMA transfer count register 0

TCR0

R/W

H'FC80 8028

H'1C80 8028

32

DMA channel control register 0

CHCR0

R/W*

3

H'FC80

802C H'1C80

802C 32

DMA source address register 1

SAR1

R/W

H'FC80 8030

H'1C80 8030

32

DMA destination address register 1

DAR1

R/W

H'FC80 8034

H'1C80 8034

32

DMA transfer count register 1

TCR1

R/W

H'FC80 8038

H'1C80 8038

32

DMA channel control register 1

CHCR1

R/W*

3

H'FC80

803C H'1C80

803C 32

DMA source address register 2

SAR2

R/W

H'FC80 8040

H'1C80 8040

32

DMA destination address register 2

DAR2

R/W

H'FC80 8044

H'1C80 8044

32

DMA transfer count register 2

TCR2

R/W

H'FC80 8048

H'1C80 8048

32

DMA channel control register 2

CHCR2

R/W*

3

H'FC80

804C H'1C80

804C 32

DMA source address register 3

SAR3

R/W

H'FC80 8050

H'1C80 8050

32

DMA destination address register 3

DAR3

R/W

H'FC80 8054

H'1C80 8054

32

DMA transfer count register 3

TCR3

R/W

H'FC80 8058

H'1C80 8058

32

DMA channel control register 3

CHCR3

R/W*

3

H'FC80

805C H'1C80

805C 32

DMA operation register 0

DMAOR0

R/W*

4

H'FC80

8060 H'1C80

8060 16

DMA source address register 4

SAR4

R/W

H'FC80 8070

H'1C80 8070

32