Renesas SH7781 User Manual

Page 346

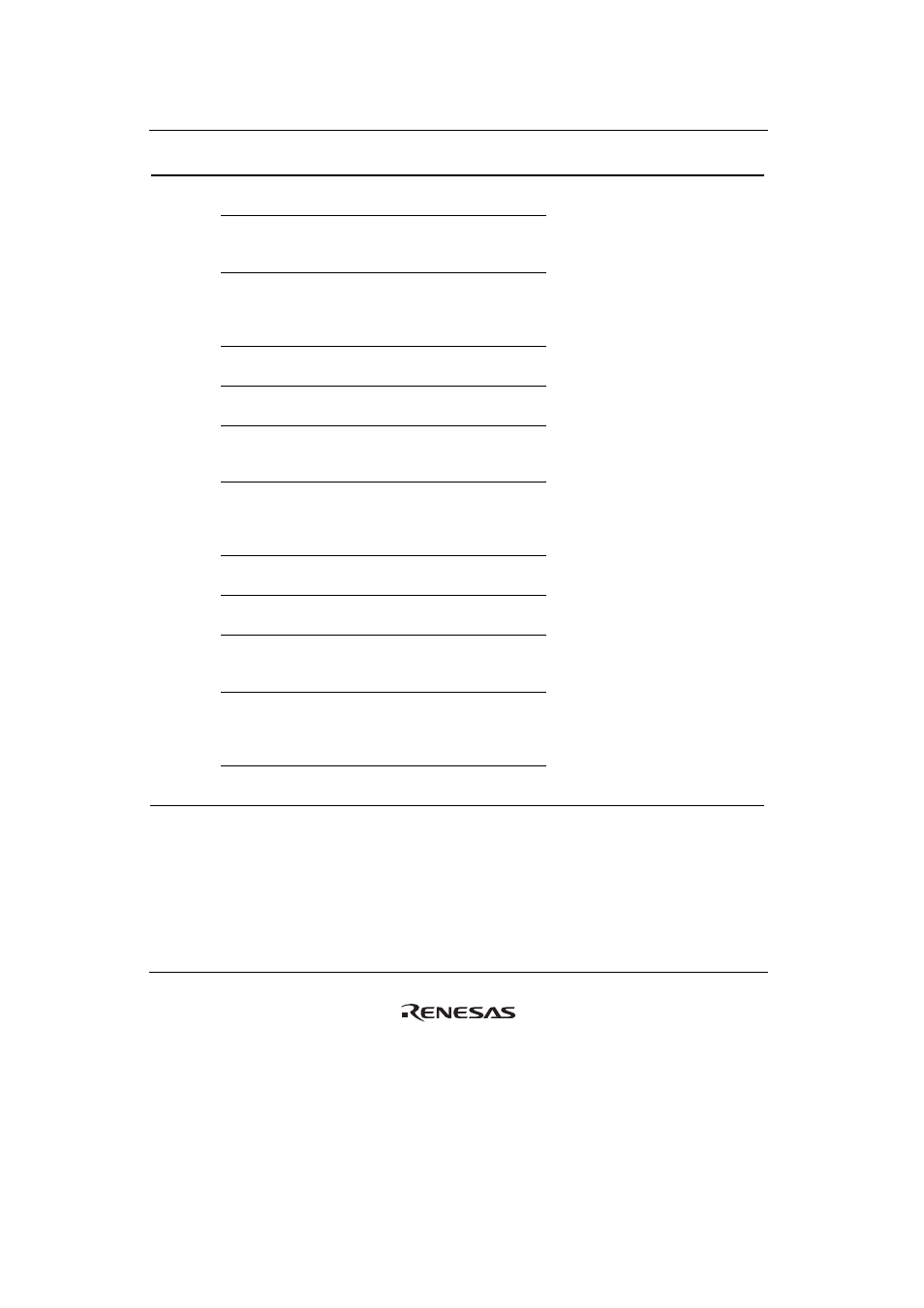

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 316 of 1658

REJ09B0261-0100

Module Bit

Name

Detailed

Source

Description

SCIF

11

TXI2

SCIF channel 2 transmit

FIFO data empty interrupt

10

BRI2

SCIF channel 2 break

interrupt or overrun error

interrupt

9

RXI2

SCIF channel 2 receive

FIFO data full interrupt or

receive data ready

interrupt

SCIF interrupt sources are

indicated. This register indicates

the SCIF interrupt sources even if

the mask setting for SCIF is made

in the interrupt mask register.

8

ERI2

SCIF channel 2 receive

error interrupt

7

TXI1

SCIF channel 1 transmit

FIFO data empty interrupt

6

BRI1

SCIF channel 1 break

interrupt or overrun error

interrupt

5

RXI1

SCIF channel 1 receive

FIFO data full interrupt or

receive data ready

interrupt

4

ERI1

SCIF channel 1 receive

error interrupt

3

TXI0

SCIF channel 0 transmit

FIFO data empty interrupt

2

BRI0

SCIF channel 0 break

interrupt or overrun error

interrupt

1

RXI0

SCIF channel 0 receive

FIFO data full interrupt or

receive data ready

interrupt

0

ERI0

SCIF channel 0 receive

error interrupt