Renesas SH7781 User Manual

Page 577

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 547 of 1658

REJ09B0261-0100

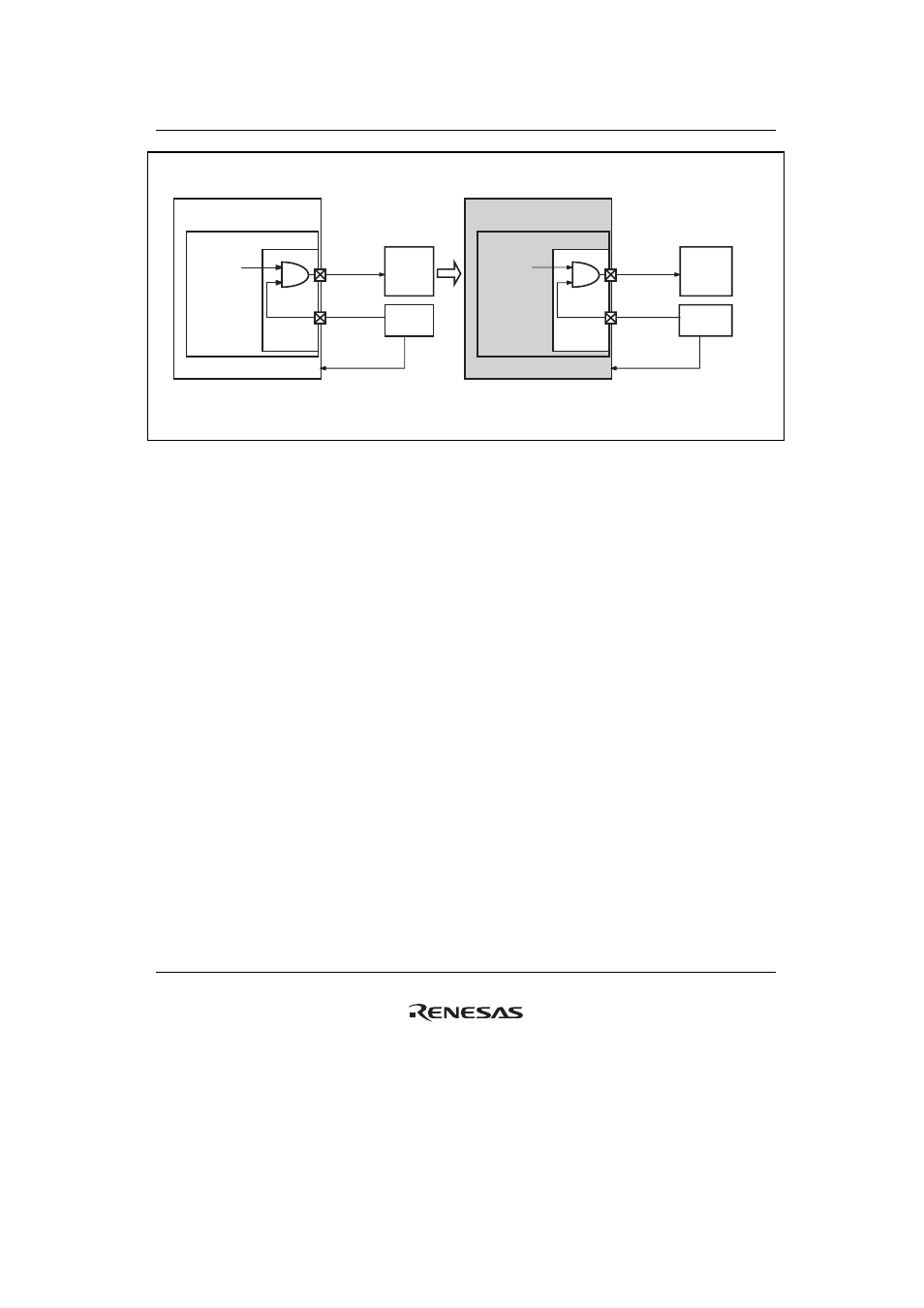

This LSI

MCKE

MBKPRST

IO cell

Internal

CKE

DBSC2

External

device

SDRAM

This LSI

MCKE

MBKPRST

IO cell

Internal

CKE

DBSC2

Low level

input

Low level

output

High level

input

1.8-V

power on

1.8-V

power on

1.0-V

power on

1.0-V

power off

Normal operation

When SDRAM power supply backup function is used

External

device

SDRAM

Normal

operation

Data is retained

in self-refresh state

Data

retained

Status signal

Status signal

As the power to most modules, except the 1.8-V

power supply for DDRPAD, is turned off, chip

power consumption can be reduced.

Figure 12.23 SDRAM Power Supply Backup Function

In order to implement the power supply backup function, a control signal

MBKPRST is necessary

to hold MCKE at low level even when power other than for the 1.8 V I/O is turned off. When this

signal is at low level, MCKE pin can be held at low level even when the power supply within the

chip is in the turned-off state. After using the DBSC2 to put the SDRAM into the self-refresh

state, by using this

MBKPRST signal to hold the MCKE signal at low level, the SDRAM self-

refresh state can be maintained even when the power supply in the chip is turned off.

To cancel the power supply backup state, perform a power-on reset. As a result, the DBSC2

registers are initialized, and so the self-refresh control circuit is also initialized. In order to put the

SDRAM into the self-refresh state before power-on reset, when the internal CKE signal is

indefinite, and also during power-on reset, the

MBKPRST signal must be held at low level.

Power-on reset causes the DBSC2 to fix the internal CKE signal at low level, so that after power-

on reset is released the

MBKPRST signal is raised to high level. (If not in the power supply

backup state,

MBKPRST is always at high level and there is no problem.)

Thus the power supply backup state is cancelled through power-on reset, and so the software must

decide whether the normal SDRAM initialization sequence is necessary, or whether the LSI was in

the power supply backup state. In order to perform this decision, a state signal is input to this LSI

from an external control circuit. The method of input is arbitrary, and a general port can be used.

After power-on reset, the software monitors the state signal applied by the external control circuit,

and judges whether the state should be the power supply backup state or whether SDRAM

initialization is necessary. Before using register settings to send MCKE to high level, the state

signal must be made to signify a state other than the power supply backup state. (After driving pin