Renesas SH7781 User Manual

Page 300

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 270 of 1658

REJ09B0261-0100

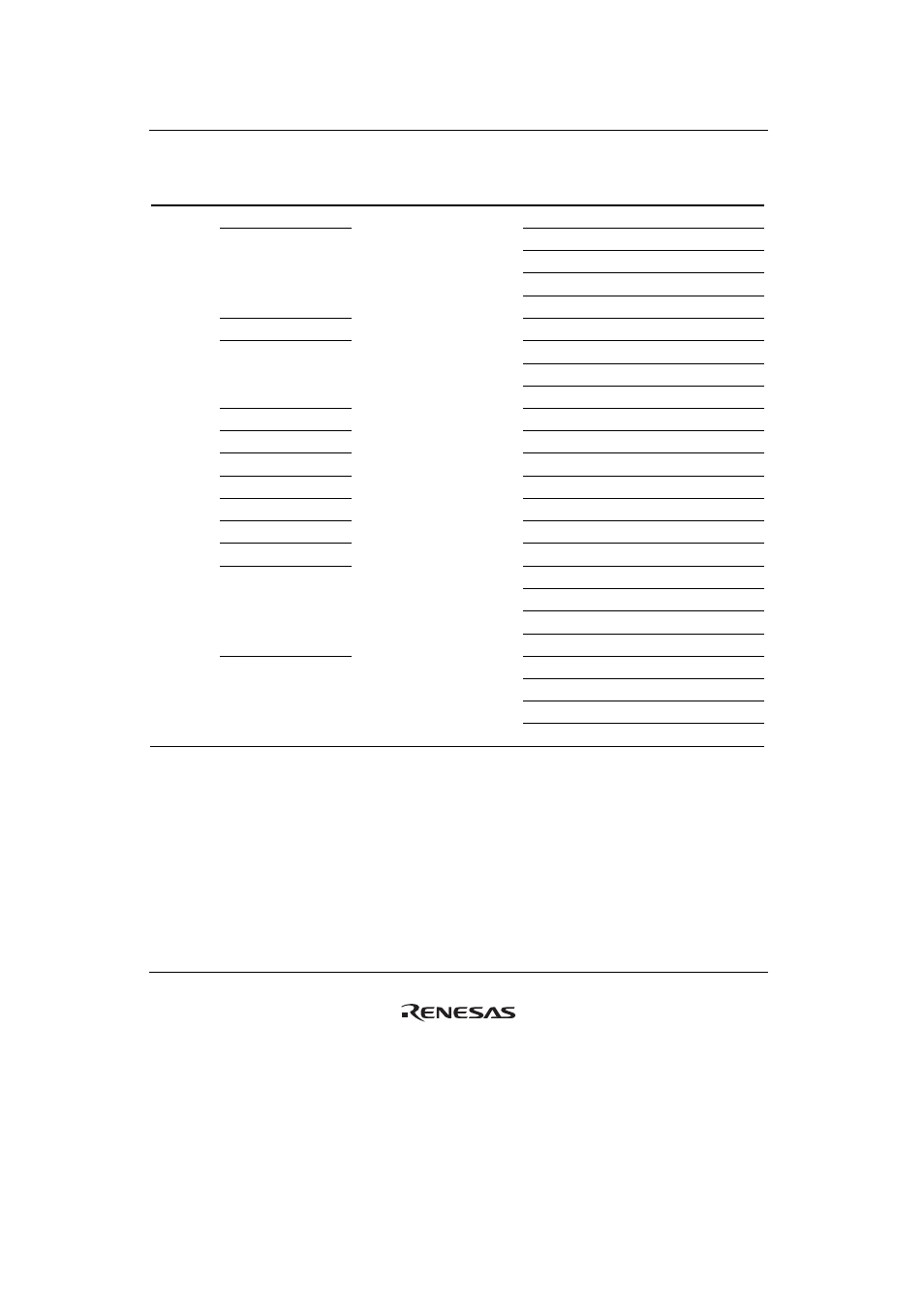

Source

Number of

Sources

(Max.) Priority

INTEVT

Remarks

SIOF 1

H'CE0 SIOFI

MMCIF 4

H'D00 FSTAT

Values set in INT2PRI0 to

INT2PRI9

H'D20 TRAN

On-chip

module

interrupts*

H'D40

ERR

H'D60

FRDY

DU

1

H'D80

DUI

GDTA

3

H'DA0

GACLI

H'DC0

GAMCI

H'DE0

GAERI

TMU-ch3

1

H'E00

TUNI3*

TMU-ch4

1

H'E20

TUNI4*

TMU-ch5

1

H'E40

TUNI5*

SSI-ch0

1

H'E80

SSII0

SSI-ch1

1

H'EA0

SSII1

HAC-ch0

1

H'EC0

HACI0

HAC-ch1

1

H'EE0

HACI1

FLCTL

4

H'F00

FLSTE*

H'F20

FLTEND*

H'F40

FLTRQ0*

H'F60

FLTRQ1*

GPIO

4

H'F80

GPIOI0 (Port pins E0 to E2)

H'FA0

GPIOI1 (Port pins E3 to E5)

H'FC0

GPIOI2 (Port pins H1 to H4)

H'FE0

GPIOI3 (Port pins L6 and L7)

Legend:

ITI:

WDT Interval timer interrupt

TUNI0 to TUNI5:

TMU channels 0 to 5 underflow interrupt

TICPI2:

TMU channel 2 input capture interrupt

DMINT0 to DMINT11:

DMAC channels 0 to 11 transfer end interrupt

DMAE0 (ch0 to 5):

DMAC address error interrupt (channels 0 to 5)

DMAE1 (ch6 to 11):

DMAC address error interrupt (channels 6 to 11)

ERI0, ERI1, ERI2,

ERI3, ERI4, ERI5:

SCIF channels 0 to 5 receive error interrupt

RXI0, RXI1, RXI2,

RXI3, RXI4, RXI5:

SCIF channels 0 to 5 receive data full interrupt