Renesas SH7781 User Manual

Page 626

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 596 of 1658

REJ09B0261-0100

(4)

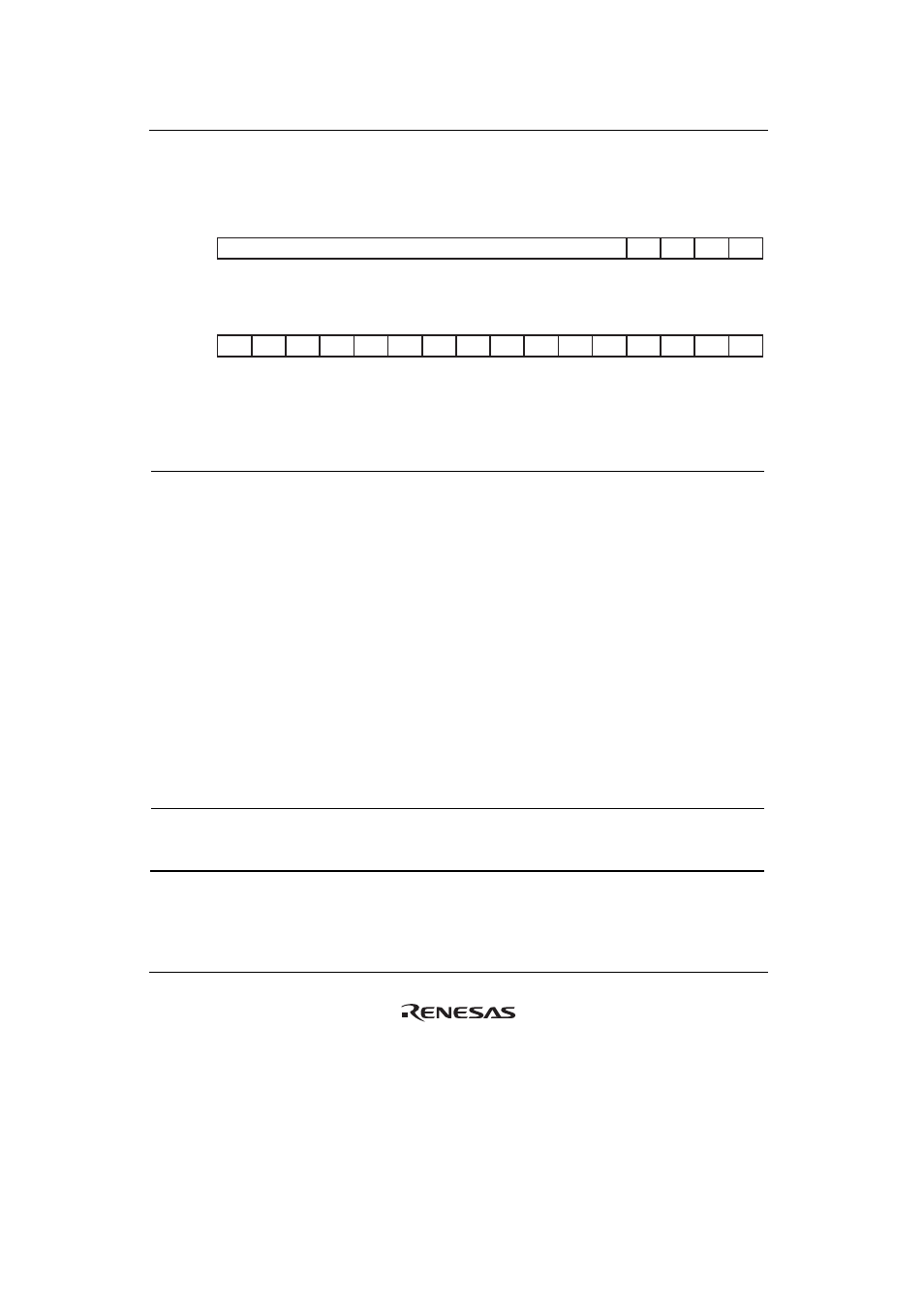

PCI Local Address Register 0 (PCILAR0)

See section 13.4.3 (2), Accessing PCI Memory Space.

SH R/W:

PCI R/W:

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

SH R/W:

PCI R/W:

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

—

—

—

—

LAR

Bit:

Initial value:

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

Bit:

Initial value:

Bit Bit

Name

Initial

Value R/W

Description

31 to 20 LAR

H'000 SH: R/W

PCI: R

Local Address (12 bits)

These bits specify bits 31 to 20 for the start address of the

local address space 0 (internal bus space in this LSI).

As shown below, the valid bits of LAR change depending on

the local address space size specified by the LSR bit in

PCILSR0.

PCILSR0.LSR ([28:20]) = B'0 0000 0000: Bits [31:20] are valid.

PCILSR0.LSR ([28:20]) = B'0 0000 0001: Bits [31:21] are valid.

PCILSR0.LSR ([28:20]) = B'0 0000 0011: Bits [31:22] are valid.

PCILSR0.LSR ([28:20]) = B'0 0000 0111: Bits [31:23] are valid.

PCILSR0.LSR ([28:20]) = B'0 0000 1111: Bits [31:24] are valid.

PCILSR0.LSR ([28:20]) = B'0 0001 1111: Bits [31:25] are valid.

PCILSR0.LSR ([28:20]) = B'0 0011 1111: Bits [31:26] are valid.

PCILSR0.LSR ([28:20]) = B'0 0111 1111: Bits [31:27] are valid.

PCILSR0.LSR ([28:20]) = B'0 1111 1111: Bits [31:28] are valid.

PCILSR0.LSR ([28:20]) = B'1 1111 1111: Bits [31:29] are valid.

19 to 0

⎯

All 0

SH: R

PCI: R

Reserved

These bits are always read as 0. The write value should

always be 0.