Renesas SH7781 User Manual

Page 1569

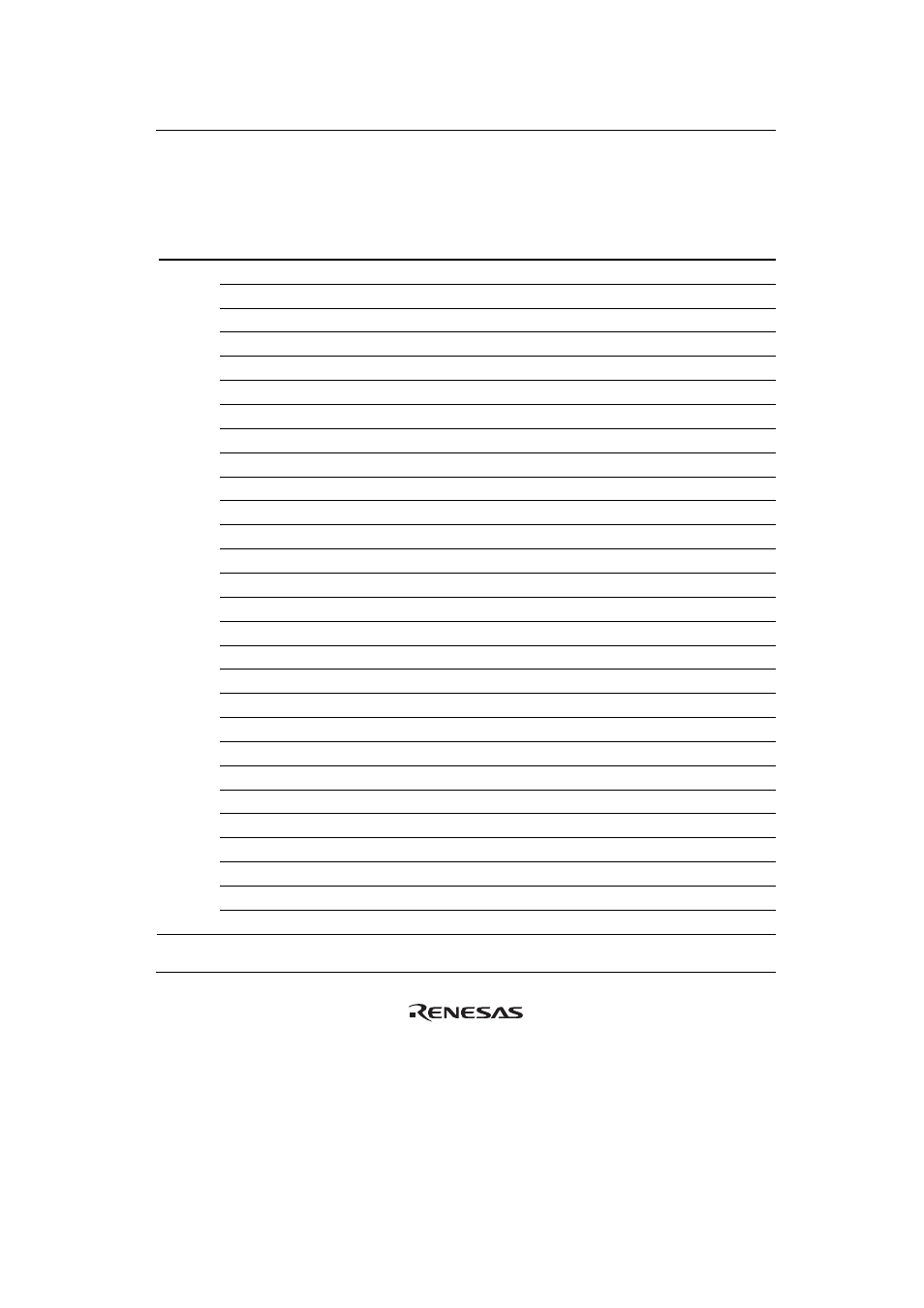

31. Register List

Rev.1.00 Jan. 10, 2008 Page 1539 of 1658

REJ09B0261-0100

Table 31.3 States of the Registers in the Individual Operating Modes (2)

Module

Name Name

Abbrev.

Power-on

Reset by

PRESET Pin/

WDT/H-UDI

Manual Reset

by

WDT/Multiple

Exception

Sleep/

Deep Sleep by

SLEEP

Instruction

Module

Standby

DMAC

DMA source address register 0

SAR0 Undefined Undefined Retained

Retained

DMA destination address register 0

DAR0

Undefined

Undefined

Retained

Retained

DMA transfer count register 0

TCR0

Undefined

Undefined

Retained

Retained

DMA channel control register 0

CHCR0

H'4000 0000

H'4000 0000

Retained

Retained

DMA source address register 1

SAR1

Undefined Undefined Retained Retained

DMA destination address register 1

DAR1

Undefined

Undefined

Retained

Retained

DMA transfer count register 1

TCR1

Undefined

Undefined

Retained

Retained

DMA channel control register 1

CHCR1

H'4000 0000

H'4000 0000

Retained

Retained

DMA source address register 2

SAR2

Undefined Undefined Retained Retained

DMA destination address register 2

DAR2

Undefined

Undefined

Retained

Retained

DMA transfer count register 2

TCR2

Undefined

Undefined

Retained

Retained

DMA channel control register 2

CHCR2

H'4000 0000

H'4000 0000

Retained

Retained

DMA source address register 3

SAR3

Undefined Undefined Retained Retained

DMA destination address register 3

DAR3

Undefined

Undefined

Retained

Retained

DMA transfer count register 3

TCR3

Undefined

Undefined

Retained

Retained

DMA channel control register 3

CHCR3

H'4000 0000

H'4000 0000

Retained

Retained

DMA operation register 0

DMAOR0 H'0000

H'0000

Retained

Retained

DMA source address register 4

SAR4

Undefined Undefined Retained Retained

DMA destination address register 4

DAR4

Undefined

Undefined

Retained

Retained

DMA transfer count register 4

TCR4

Undefined

Undefined

Retained

Retained

DMA channel control register 4

CHCR4

H'4000 0000

H'4000 0000

Retained

Retained

DMA source address register 5

SAR5

Undefined Undefined Retained Retained

DMA destination address register 5

DAR5

Undefined

Undefined

Retained

Retained

DMA transfer count register 5

TCR5

Undefined

Undefined

Retained

Retained

DMA channel control register 5

CHCR5

H'4000 0000

H'4000 0000

Retained

Retained

DMA source address register B0

SARB0 Undefined

Undefined

Retained

Retained

DMA destination address register B0 DARB0

Undefined

Undefined

Retained

Retained

DMA transfer count register B0

TCRB0

Undefined

Undefined

Retained

Retained