23 mc frame width setting register (mcwr) – Renesas SH7781 User Manual

Page 1034

20. Graphics Data Translation Accelerator (GDTA)

Rev.1.00 Jan. 10, 2008 Page 1004 of 1658

REJ09B0261-0100

Bit Bit

Name

Initial

Value R/W Description

2 to 0

MC_CFS

All 0

R

Command pointer status display

000: MCCF command parameter 1 setting wait state

001: MCCF command parameter 2 setting wait state

010: MCCF command parameter 3 setting wait state

011: MCCF command parameter 4 setting wait state

100: MCCF command parameter 5 setting wait state

101: MCCF command parameter 6 setting wait state

110: MCCF command parameter 7 setting wait state

111: MCCF command parameter 8 setting wait state

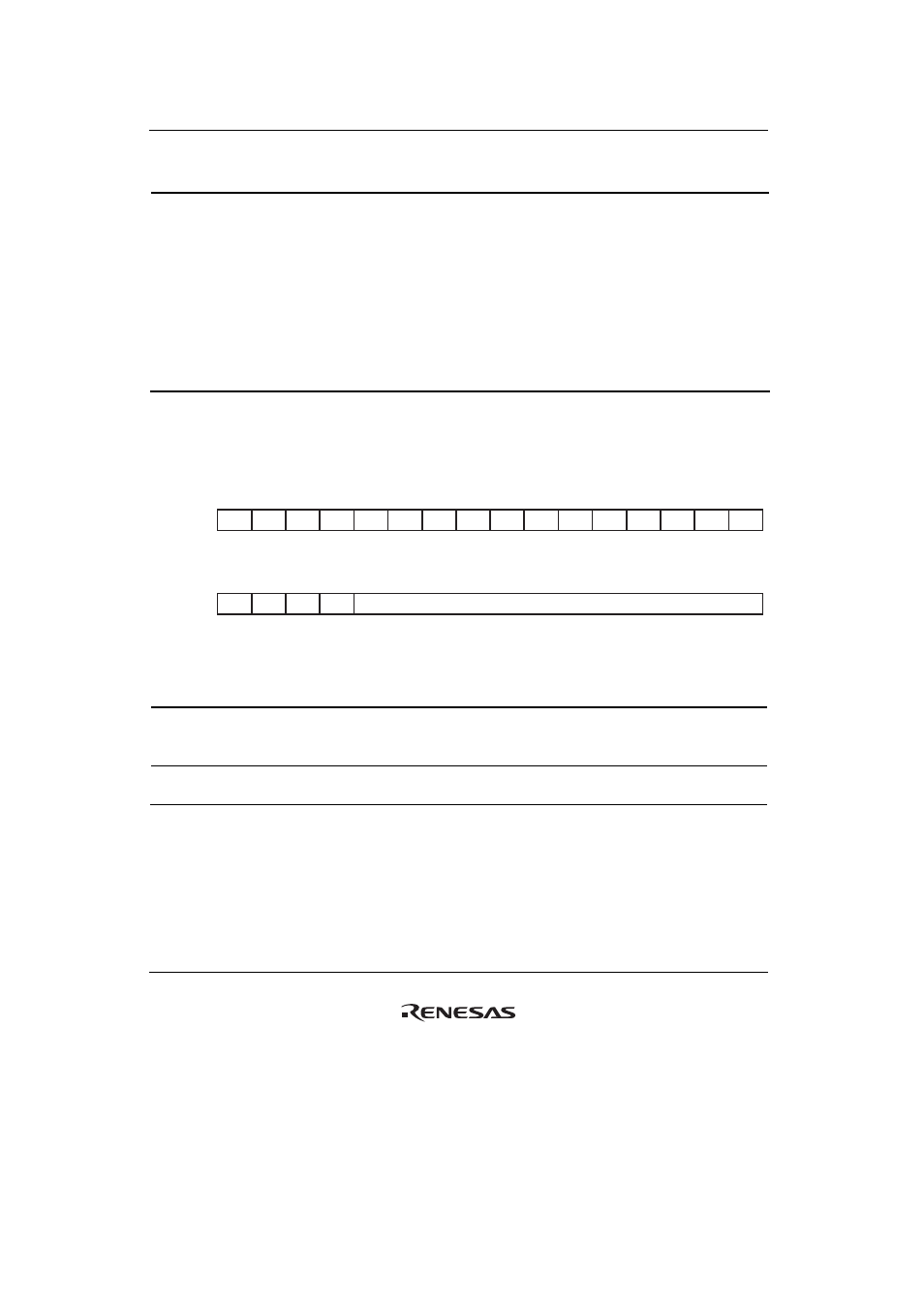

20.3.23

MC Frame Width Setting Register (MCWR)

MCWR is in the MC register block and sets the input frame width in pixel units.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

MC_W

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

⎯

⎯

⎯

⎯

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W Description

31 to 12

⎯ All

0

⎯ Reserved

These bits are always read as 0. The write value should

always be 0.

11 to 0 MC_W

All 0

R/W

Frame width setting

Should be set by the number of pixels.

Notes: 1. MC processing is prohibited when the setting is 0.

2. Addition is performed taking that 1 pixel = 1 byte.

3. MCWR (bytes) + MCYPR (bytes) should be 16 bytes x n (n: an integer greater than 0)

4. MCWR (bytes)/2 + MCUVPR (bytes) should be 8 bytes x n (n: an integer greater than

0)

5. MCWR (bytes)/2: Shifts the MCWR setting one bit to the right. (When the setting is odd,

the bit 0 setting is discarded.)