Renesas SH7781 User Manual

Page 243

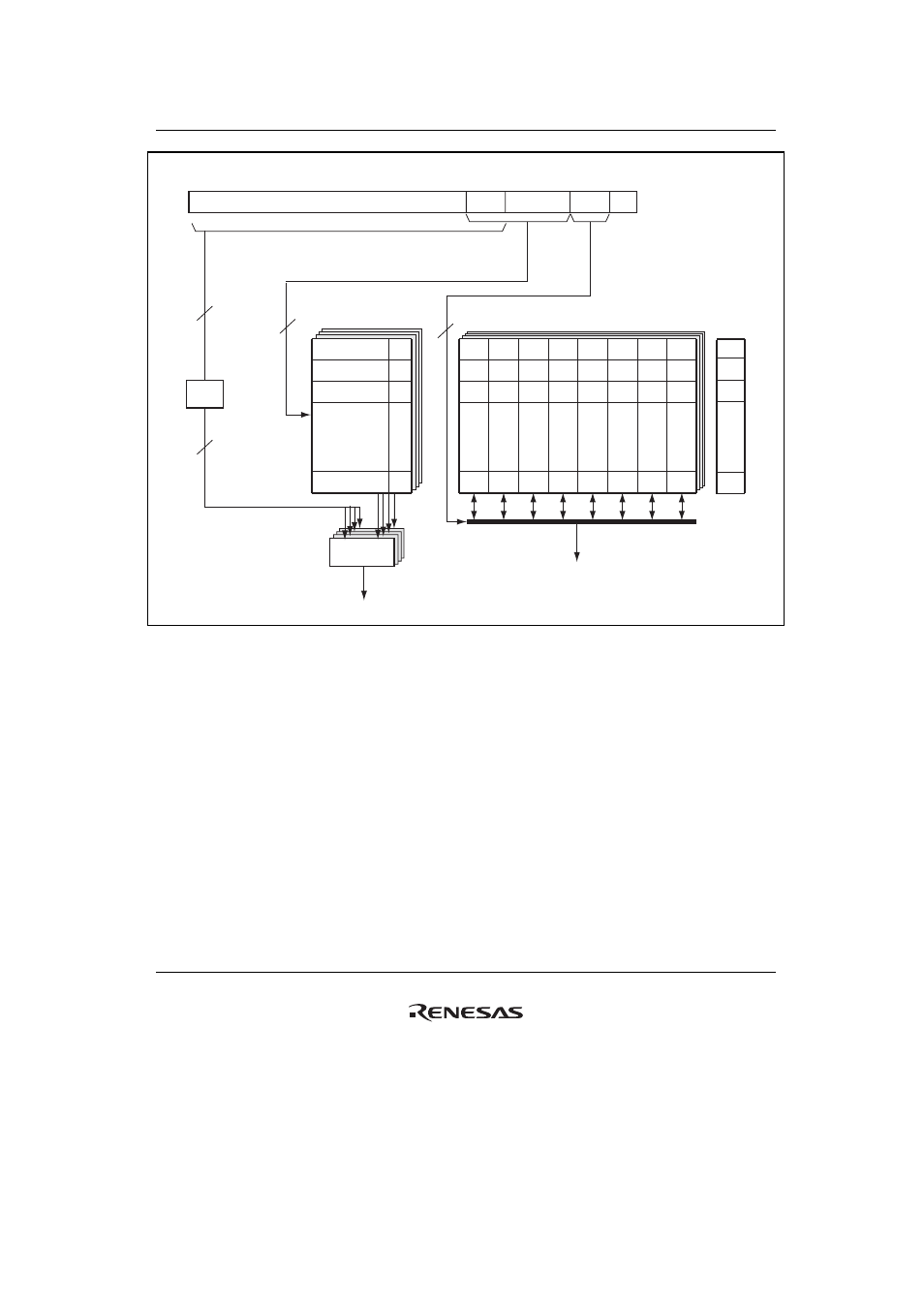

8. Caches

Rev.1.00 Jan. 10, 2008 Page 213 of 1658

REJ09B0261-0100

31

5 4

2

LW0

32 bits

LW1

32 bits

LW2

32 bits

LW3

32 bits

LW4

32 bits

LW5

32 bits

LW6

32 bits

LW7

32 bits

MMU

[12:5]

255

19 bits

1 bit

Tag

V

Address array

(way 0 to way 3)

Data array

(way 0 to way3)

Entry selection

Longword (LW) selection

Virtual address

3

8

22

19

0

Read data

13 12

10

0

6 bits

LRU

Hit signal

(Way 0 to way 3)

Comparison

Figure 8.2 Configuration of Instruction Cache (Cache size = 32 Kbytes)

• Tag

Stores the upper 19 bits of the 29-bit physical address of the data line to be cached. The tag is

not initialized by a power-on or manual reset.

• V bit (validity bit)

Indicates that valid data is stored in the cache line. When this bit is 1, the cache line data is

valid. The V bit is initialized to 0 by a power-on reset, but retains its value in a manual reset.

• U bit (dirty bit)

The U bit is set to 1 if data is written to the cache line while the cache is being used in copy-

back mode. That is, the U bit indicates a mismatch between the data in the cache line and the

data in external memory. The U bit is never set to 1 while the cache is being used in write-

through mode, unless it is modified by accessing the memory-mapped cache (see section 8.6,

Memory-Mapped Cache Configuration). The U bit is initialized to 0 by a power-on reset, but

retains its value in a manual reset.