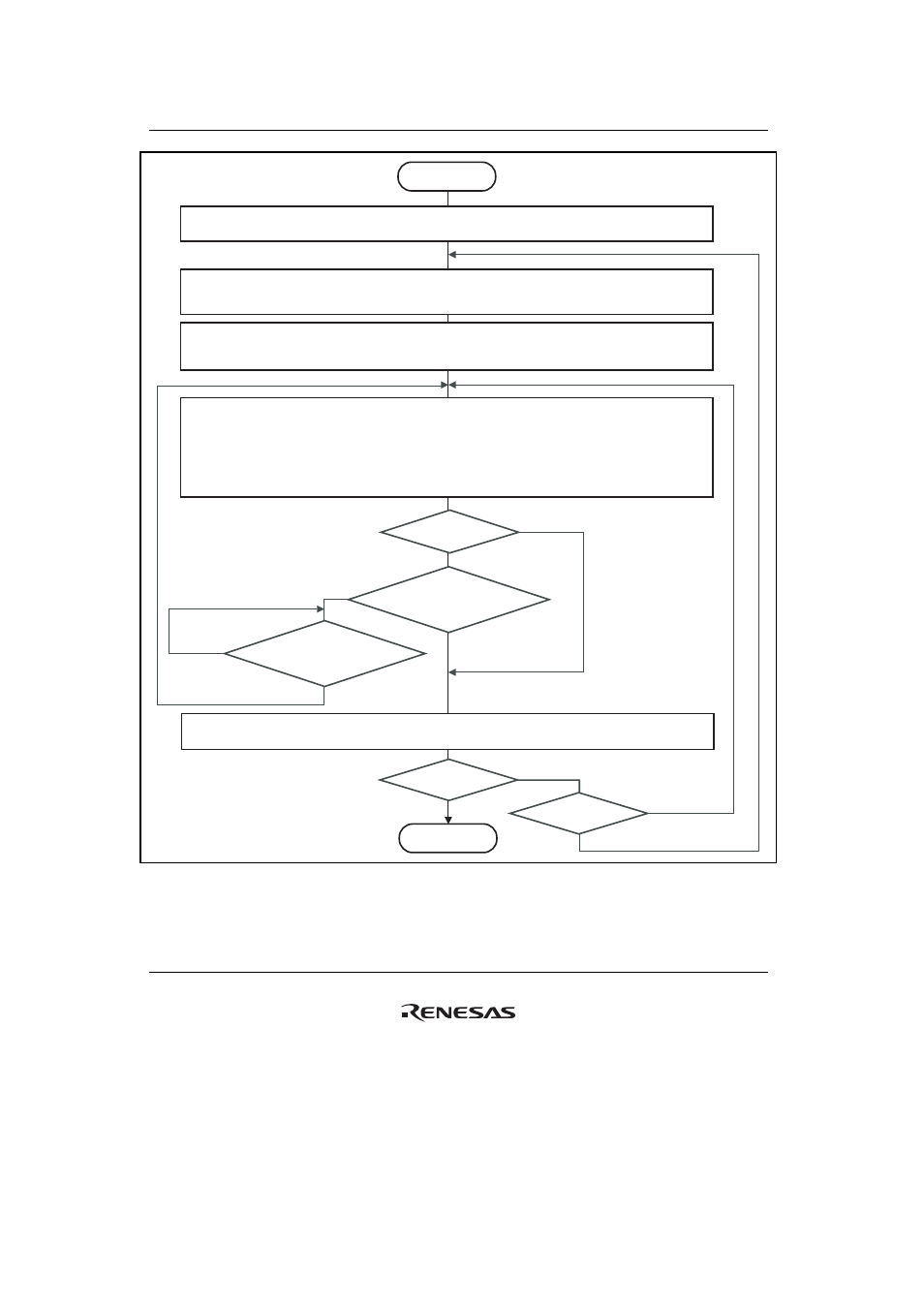

Figure 20.5 cl processing procedure – Renesas SH7781 User Manual

Page 1048

20. Graphics Data Translation Accelerator (GDTA)

Rev.1.00 Jan. 10, 2008 Page 1018 of 1658

REJ09B0261-0100

[Step (1) Clear the CL access mask]

After the CPU sets the key code in GACMR within the bus interface, set GACER to enable access to the CL function block.

[Step (2) Initialize the CL function block]

The CPU sets the frame width/height, input Y/UV padding size, output padding size, and output data/address mode.

In ARGB conversion mode, CLPLPR should also be set.

[Step (5) Wait for processing completion]

Processing completion is judged using an interrupt from the CPU or the CL_END bit in GACISR.

[Step (3) Write the color conversion table to RAM 0]

The CPU writes the color conversion table to RAM 0.

* Step (3) is not necessary in YUYV conversion mode; it is only required in ARGB conversion mode.

[Step (4) Write to the command FIFO]

The CPU writes commands to CLCF. Four command parameters are required

and should be written in succession in the following order:

(1) Data for writing: Input Y pointer

(2) Data for writing: Input U pointer

(3) Data for writing: Input V pointer

(4) Data for writing: Output pointer

Continuous processing?

Next processing?

End

Start

Is continuous processing

timed by interrupt or setting of the

CL_END bit in GACISR?

Is the CL command FIFO full?

(Check the CK_CFF bit in CLSR.)

Change settings

for CL processing?

No

No

No

No

No

Yes

Yes

Yes

Yes

Yes

Figure 20.5 CL Processing Procedure