Figure 14.1 shows a block diagram of the dmac, Figure 14.1 block diagram of dmac – Renesas SH7781 User Manual

Page 696

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 666 of 1658

REJ09B0261-0100

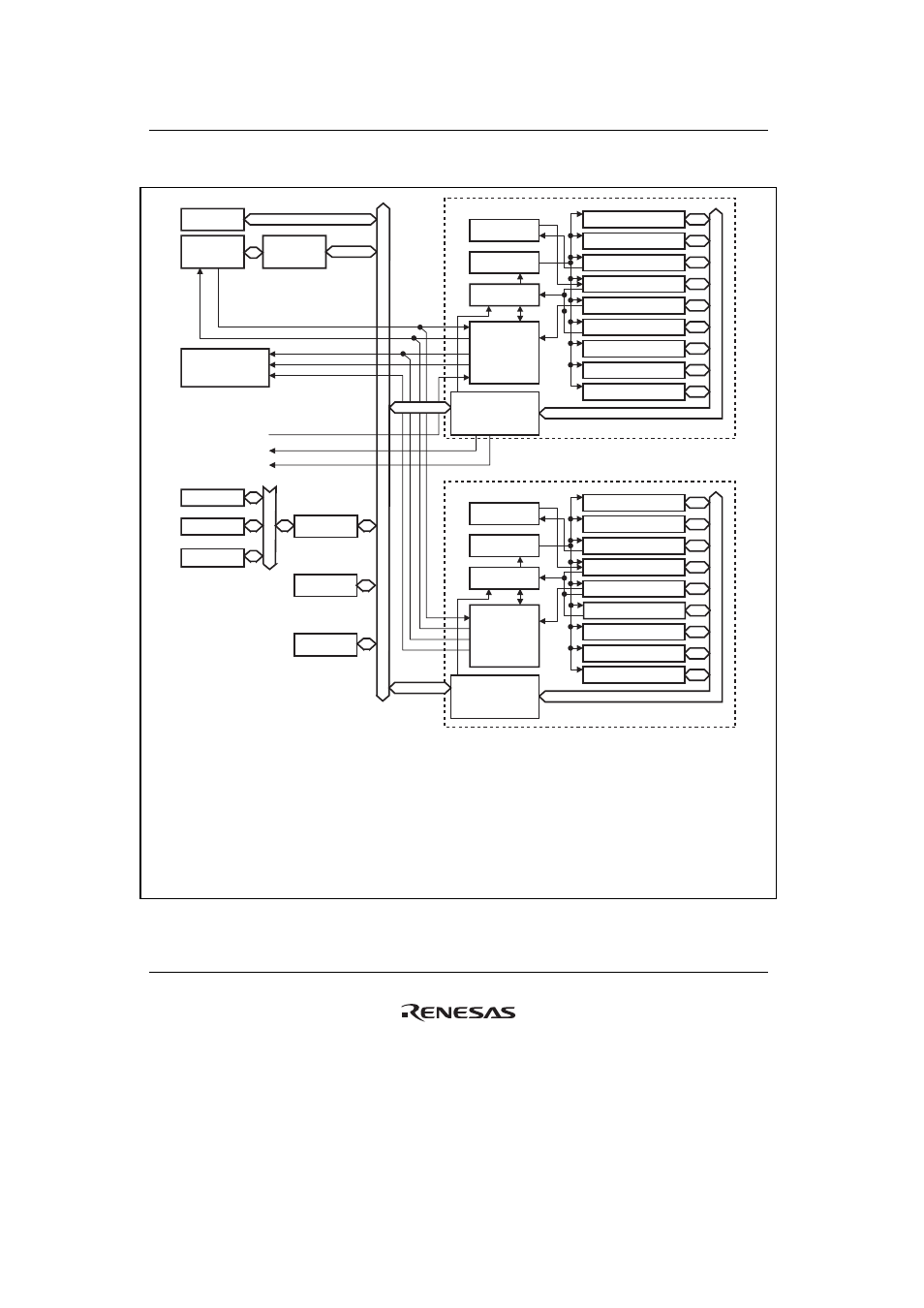

Figure 14.1 shows a block diagram of the DMAC.

Peripheral

bus controller

DMA transfer end signal

Iteration

control

DMAC channels 6 to 11

Register

control

Start-up

control

Request

priority

control

Bus

interface

Iteration

control

DMAC channels 0 to 5

Register

control

Start-up

control

Request

priority

control

Bus

interface

On-chip

memory

On-chip

peripheral

module

Interrupt controller

DMA transfer request signal

External ROM

External RAM

External I/O

TCR0 to TCR5

CHCR0 to CHCR5

DMAOR0

DMARS0 to DMARS2

SAR0 to SAR5

DAR0 to DAR5

TCRB0 to TCRB3

SARB0 to SARB3

DARB0 to DARB3

DMINT0 to DMINT11

DMAE0

DMAE1

DRAK0 to DRAK3

DREQ0 to DREQ3

DACK0 to DACK3

LBSC

DDRIF

PCIC

TCR6 to TCR11

CHCR6 to CHCR11

DMAOR1

SAR6 to SAR11

DAR6 to DAR11

TCRB6 to TCRB9

SARB6 to SARB9

DARB6 to DARB9

DMARS3 to DMARS5

Legend:

SAR0 to SAR11:

DMA source address register

SARB0 to SARB3, SARB6 to SARB11:

DMA source address register B

DAR0 to DAR11:

DMA destination address register

DARB0 to DARB3, DARB6 to DARB9:

DMA destination address register B

TCR0 to TCR11:

DMA transfer count register

TCRB0 to TCRB3, TCRB6 to TCRB9:

DMA transfer count register B

CHCR0 to CHCR11:

DMA channel control register

DMAOR0 and DMAOR1:

DMA operation register

DMARS0 to DMARS5:

DMA extended resource register

DMINT0 to DMINT11:

DMA transfer end/half-end interrupt request*

DMAE0:

channels 0 to 5 address error interrupt request

DMAE1:

channels 6 to 11 address error interrupt request

Note: * The half-end interrupt request is valid for only channels 0 to 3 and channels 6 to 9.

SuperHyway bus

Figure 14.1 Block Diagram of DMAC