Renesas SH7781 User Manual

Page 420

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 390 of 1658

REJ09B0261-0100

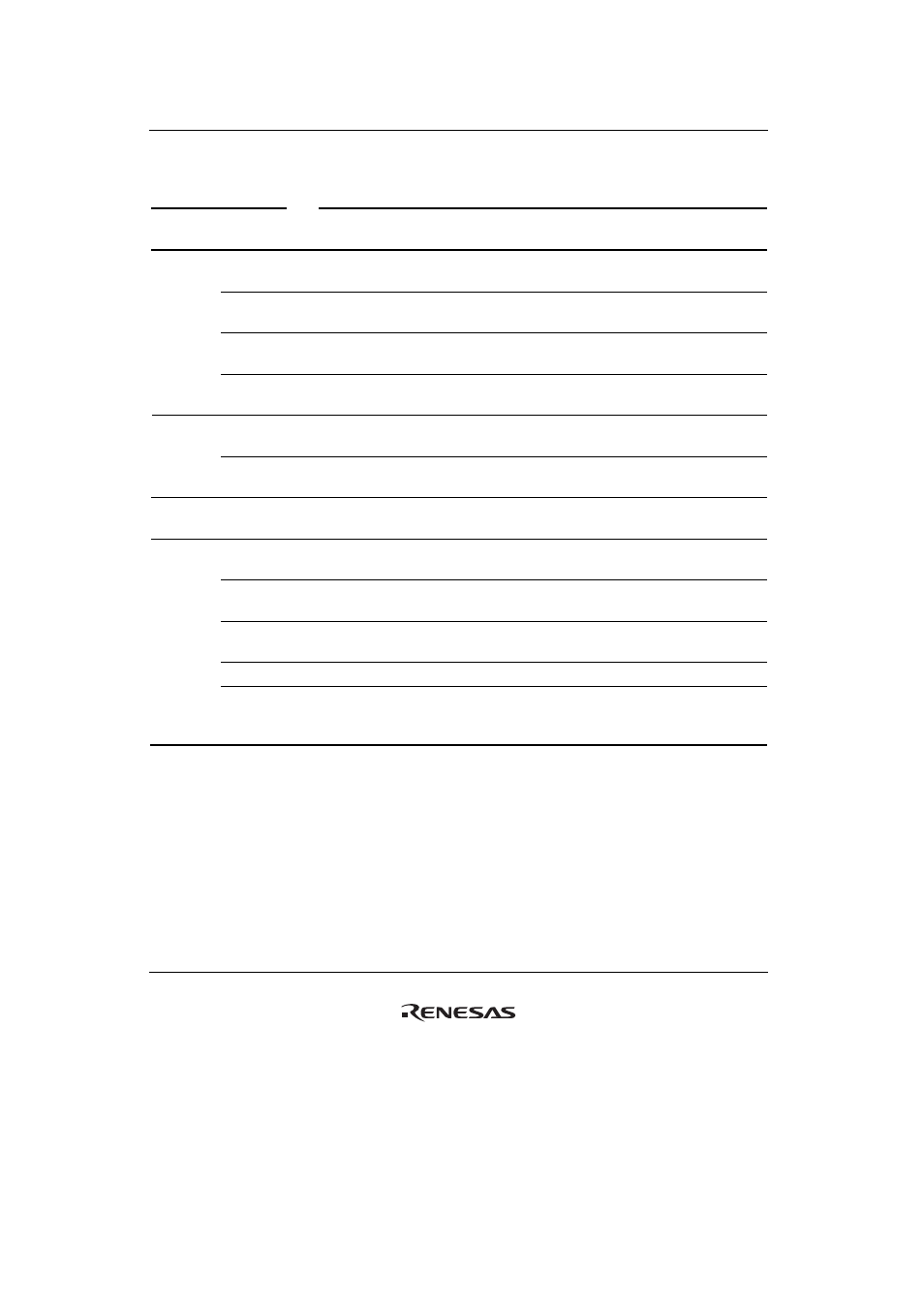

Table 11.8 32-Bit External Device/Big-Endian Access and Data Alignment

Operation

Data Bus

Strobe Signals

Access

Size Address

No.

D31 to

D24

D23 to

D16

D15 to

D8

D7 to

D0

WE3 WE2 WE1 WE0

4n 1

Data

7 to 0

⎯

⎯

⎯ Asserted

4n + 1

1

⎯ Data

7 to 0

⎯

⎯ Asserted

4n + 2

1

⎯

⎯ Data

7 to 0

⎯

Asserted

Byte

4n + 3

1

⎯

⎯

⎯ Data

7 to 0

Asserted

4n 1

Data

15 to 8

Data

7 to 0

⎯

⎯ Asserted Asserted

Word

4n + 2

1

⎯

⎯ Data

15 to 8

Data

7 to 0

Asserted

Asserted

Longword 4n

1 Data

31 to 24

Data

23 to 16

Data

15 to 8

Data

7 to 0

Asserted Asserted Asserted Asserted

32 Bytes* 8n

1 Data

31 to 24

Data

23 to 16

Data

15 to 8

Data

7 to 0

Asserted Asserted Asserted Asserted

8n + 4

2

Data

63 to 56

Data

55 to 48

Data

47 to 40

Data

39 to 32

Asserted Asserted Asserted Asserted

8n + 8

3

Data

95 to 88

Data

87 to 80

Data

79 to 72

Data

71 to 64

Asserted Asserted Asserted Asserted

…

…

…

…

…

…

…

…

…

…

8n + 28

8

Data

255 to

248

Data

247 to

240

Data

239 to

232

Data

231 to

224

Asserted Asserted Asserted Asserted

Note: * This table shows an example when the access start address is on the 32-byte

boundary. When the start address is not on the 32-byte boundary, accesses are

performed up to immediately before the 32-byte boundary and the address is wrapped

around to the previous 32-byte boundary.