6 serial control register (scscr) – Renesas SH7781 User Manual

Page 1081

21. Serial Communication Interface with FIFO (SCIF)

Rev.1.00 Jan. 10, 2008 Page 1051 of 1658

REJ09B0261-0100

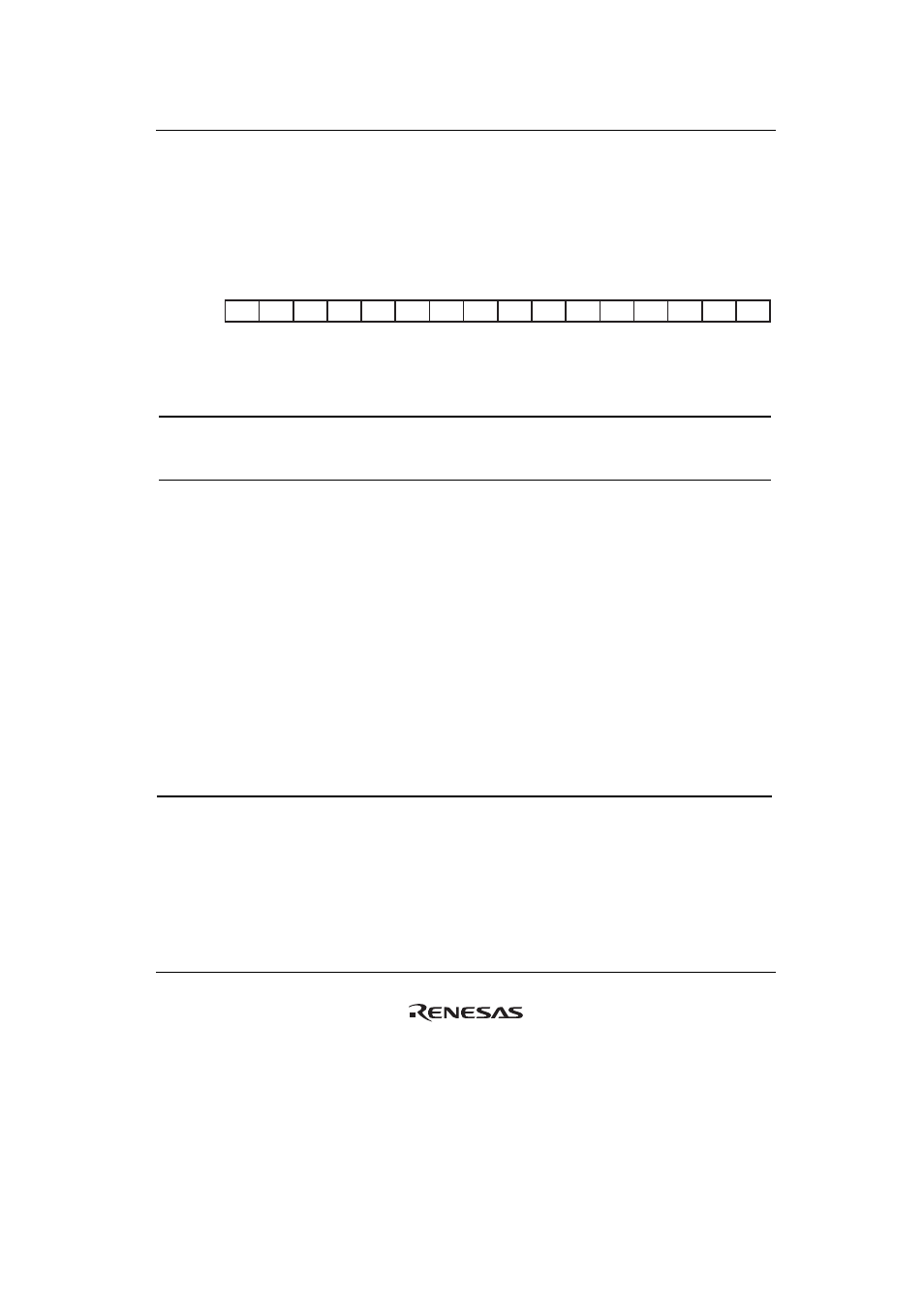

21.3.6

Serial Control Register (SCSCR)

SCSCR is a register used to enable/disable transmission/reception by SCIF, serial clock output,

interrupt requests, and to select transmission/reception clock source for the SCIF.

SCSCR can always be read from and written to by the CPU.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

CKE0

CKE1

⎯

REIE

RE

TE

RIE

TIE

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

15 to 8

—

All 0

R

Reserved

These bits are always read as 0. The write value

should always be 0.

7

TIE

0

R/W

Transmit Interrupt Enable

Enables or disables transmit-FIFO-data-empty interrupt

(TXI) request generation when serial transmit data is

transferred from SCFTDR to SCTSR, the number of

data bytes in SCFTDR falls to or below the transmit

trigger setting count, and the TDFE flag in SCFSR is

set to 1.

TXI interrupt requests can be released by the following

methods: Either by reading 1 from the TDFE flag in

SCFSR, writing transmit data exceeding the transmit

trigger setting count to SCFTDR and then clearing the

TDFE flag in SCFSR to 0, or by clearing the TIE bit to

0.

0: Transmit-FIFO-data-empty interrupt (TXI) request

disabled

1: Transmit-FIFO-data-empty interrupt (TXI) request

enabled