5 status pin change timing during reset, 1 power-on reset by preset pin – Renesas SH7781 User Manual

Page 804

16. Watchdog Timer and Reset (WDT)

Rev.1.00 Jan. 10, 2008 Page 774 of 1658

REJ09B0261-0100

16.5

Status Pin Change Timing during Reset

16.5.1

Power-On Reset by

PRESET Pin

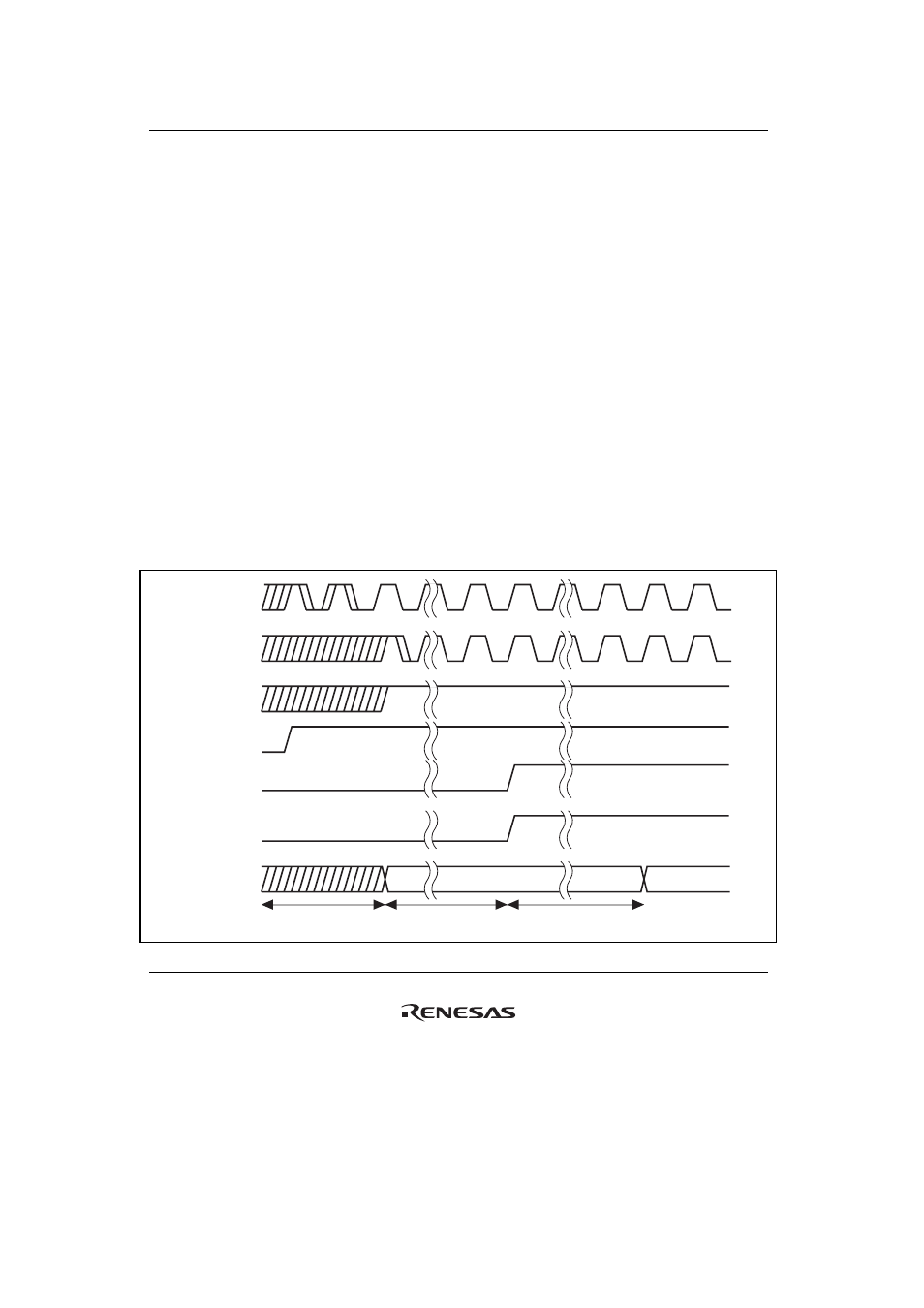

Since the PLL circuit is initialized when the LSI enters the power-on reset state, the PLL

oscillation settling time needs to be ensured. This means that a high level must not be input to the

PRESET pin during the PLL oscillation settling time. The PLL oscillation settling time is the sum

of the settling times for PLL1 and PLL2.

After the state on the

PRESET pin input is changed from a low level to high level, the internal

reset state continues until the reset holding time elapses. The reset holding time is equal to or more

than 40 cycles of the peripheral clock (Pck).

(1)

When the Power Is Turned On

When the power is turned on, ensure that a low level is input to the

PRESET pin. A low level

input is also needed on the

TRST pin to initialize the H-UDI.

The timing of reset state indication on the STATUS[1:0] pins is asynchronous. On the other hand,

the timing of indicating normal operation is synchronous with the peripheral clock (Pck), and is

therefore asynchronous with the clocks input from the EXTAL pin and the CLKOUT pin.

VDD

TRST

input

PRESET

input

CLKOUT

output

STATUS[1:0]

output

HH (reset)

LL (normal)

EXTAL input

stabilization time

PLL oscillation

settling time

Reset holding time

EXTAL

input

CLKOUTENB

output

Figure 16.3 STATUS Output when Power Is Turned On