Renesas SH7781 User Manual

Page 381

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 351 of 1658

REJ09B0261-0100

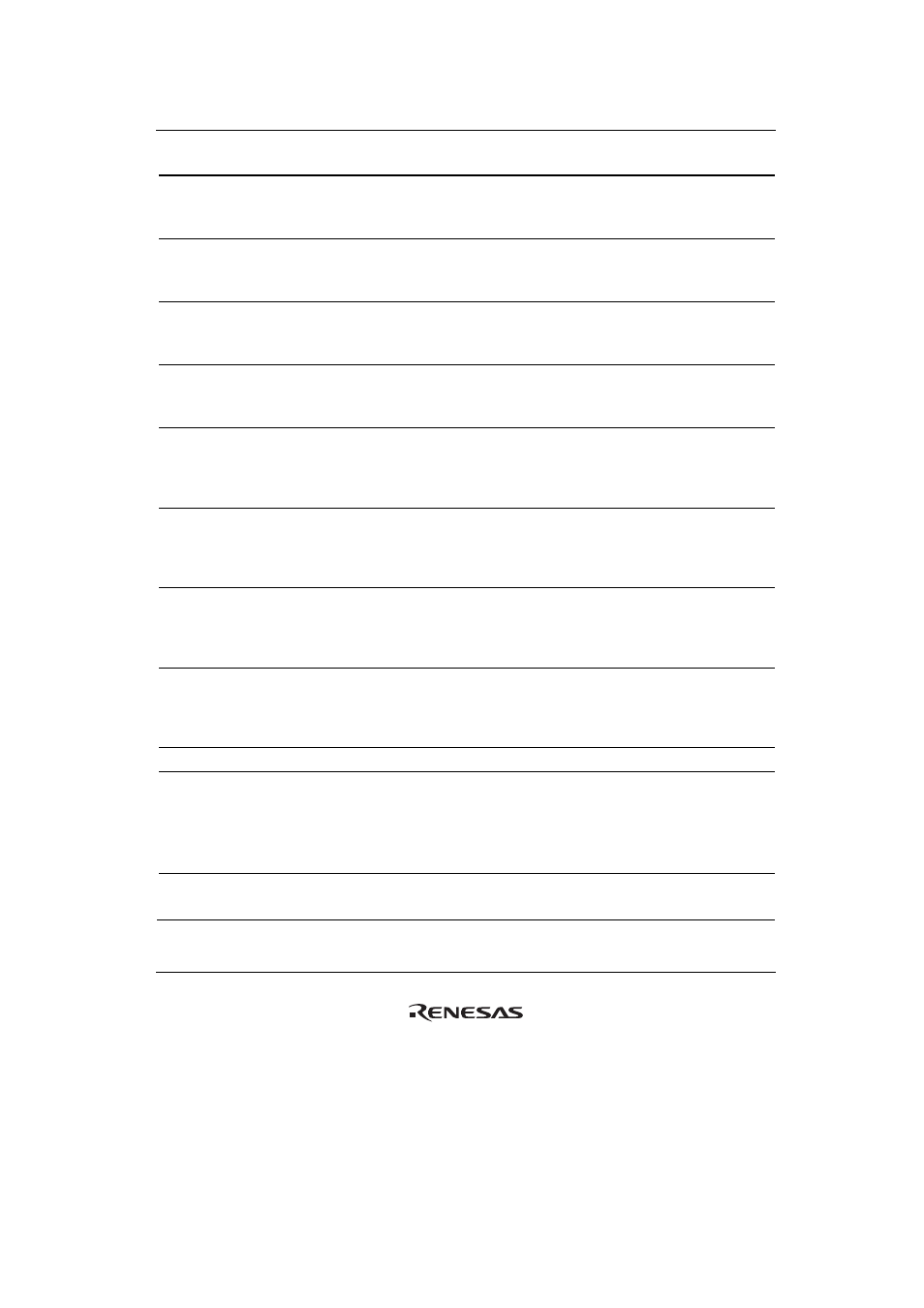

Pin Name

Function

I/O

Description

WE0/REG

Data Enable 0

O

Write strobe signal for D7 to D0 in SRAM

interface setting

REG signal in PCMCIA interface setting

WE1

Data Enable 1

O

Write strobe signal for D15 to D8 in SRAM

interface setting

Write strobe signal in PCMCIA interface setting

WE2/IORD

Data Enable 2

O

Write strobe signal for D23 to D16 in SRAM

interface setting

IORD signal in PCMCIA interface setting

WE3/IOWR

Data Enable 3

O

Write strobe signal for D31 to D24 in SRAM

interface setting

IOWR signal in PCMCIA interface setting

WE4

Data Enable 4

O

Write strobe signal for D39 to D32 in SRAM

interface setting

Multiplexed with PCI/Port R0 (GPIO

input/output).

WE5

Data Enable 5

O

Write strobe signal for D47 to D40 in SRAM

interface setting

Multiplexed with PCI/Port R1 (GPIO

input/output).

WE6

Data Enable 6

O

Write strobe signal for D55 to D48 in SRAM

interface setting

Multiplexed with PCI/Port R2 (GPIO

input/output).

WE7

Data Enable 7

O

Write strobe signal for D63 to D56 in SRAM

interface setting

Multiplexed with PCI/Port R3 (GPIO

input/output).

RDY

Ready

I

Wait cycle request signal

IOIS16

16-Bit I/O

I

16-bit I/O designation signal in PCMCIA

interface setting

Valid only in little endian mode

Multiplexed with MODE13, TCLK (TMU

input/output), and Port J0 (GPIO input/output)

BREQ

Bus Release

Request

I

Bus release request signal

Multiplexed with Port M1 (GPIO input/output).