Renesas SH7781 User Manual

Page 365

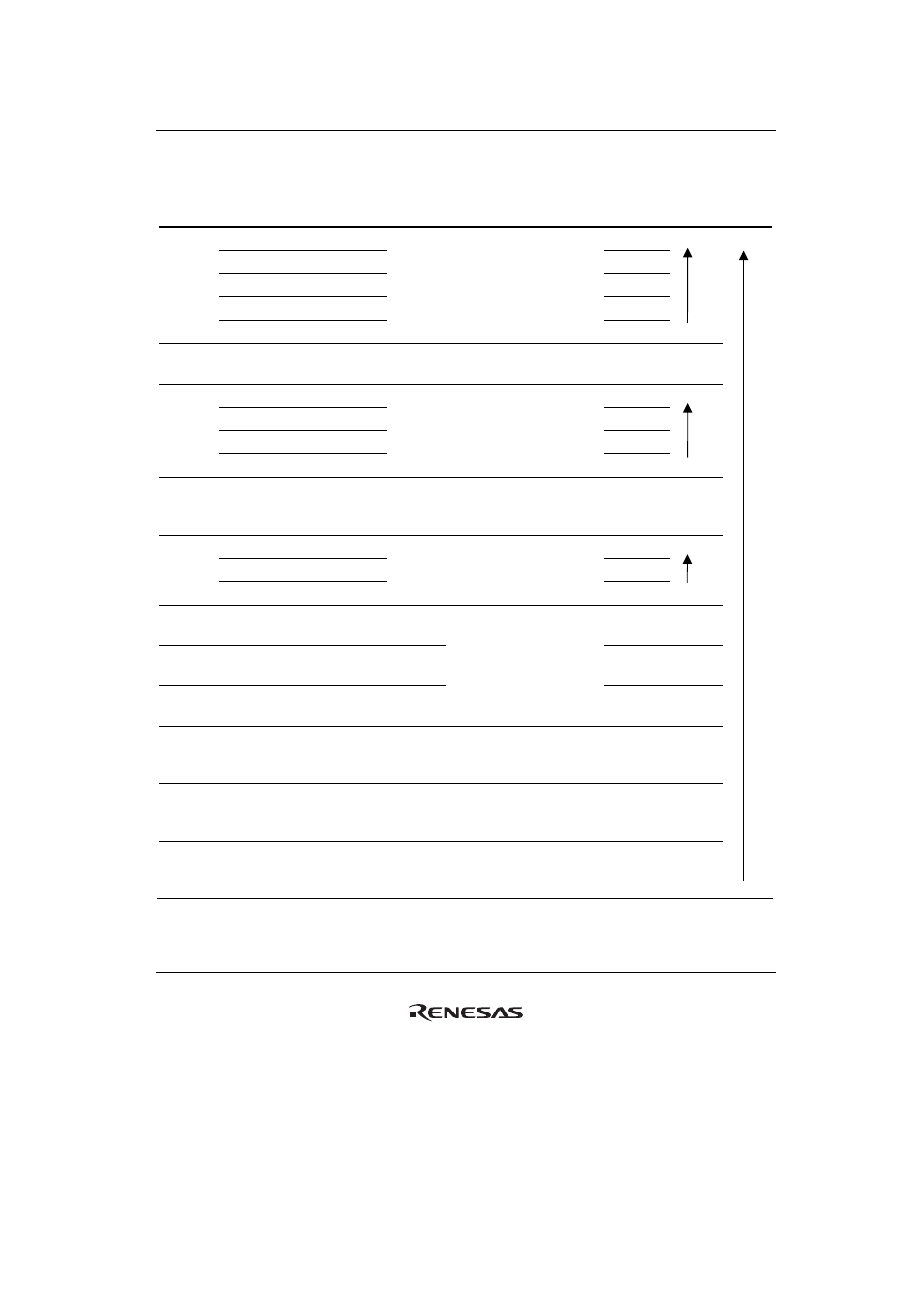

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 335 of 1658

REJ09B0261-0100

Interrupt Source

INTEVT

Code

Interrupt

Priority

Mask/Clear

Register & Bit

Interrupt

Source

Register

Detail

Source

Register

Priority

within

Sets of

Sources

Default

Priority

PCIC(5) PCIERR

H'AA0

INT2B4[5] High

High

PCIPWD3 H'AC0

INT2B4[6]

PCIPWD2 H'AC0

INT2PRI6

[4:0]

INT2MSKR[19]

INT2MSKCLR

[19]

INT2A0[19]

INT2A1[19]

INT2B4[7]

PCIPWD1 H'AC0

INT2B4[8]

PCIPWD0 H'AE0

INT2B4[9]

Low

SIOF SIOFI

H'CE0

INT2PRI6

[28:24]

INT2MSKR[20]

INT2MSKCR[20]

INT2A0[20]

INT2A1[20]

⎯

MMCIF FSTAT

H'D00

INT2B4[0]

High

TRAN

H'D20

INT2B4[1]

ERR

H'D40

INT2PRI6

[12:8]

INT2MSKR[22]

INT2MSKCLR

[22]

INT2A0[22]

INT2A1[22]

INT2B4[2]

FRDY

H'D60

INT2B4[3]

Low

DU DUI

H'D80

INT2PRI9

[28:24]

INT2MSKR[27]

INT2MSKCLR

[27]

INT2A0[27]

INT2A1[27]

GDTA GACLI

H'DA0

INT2B7[0]

High

GAMCI

H'DC0

INT2B7[1]

GAERI

H'DE0

INT2PRI9

[20:16]

INT2MSKR[28]

INT2MSKCLR

[28]

INT2A0[28]

INT2A1[28]

INT2B7[2] Low

TMU-ch3 TUNI3* H'E00

INT2PRI1

[28:24]

INT2MSKR[1]

INT2MSKCLR[1]

INT2A0[1]

INT2A1[1]

INT2B0[4]

TMU-ch4 TUNI4* H'E20

INT2PRI1

[20:16]

INT2B0[5]

TMU-ch5 TUNI5* H'E40

INT2PRI1

[12:8]

INT2B0[6]

SSI-ch0 SSII0

H'E80 INT2PRI8

[12:8]

INT2MSKR[25]

INT2MSKCLR

[25]

INT2A0[25]

INT2A1[25]

⎯

SSI-ch1 SSII1

H'EA0 INT2PRI6

[4:0]

INT2MSKR[26]

INT2MSKCLR

[26]

INT2A0[26]

INT2A1[26]

⎯

HAC-ch0 HACI0

H'EC0 INT2PRI6

[28:24]

INT2MSKR[12]

INT2MSKCLR

[12]

INT2A0[12]

INT2A1[12]

⎯

Low