Figure 4.2 instruction execution patterns (1) – Renesas SH7781 User Manual

Page 97

4. Pipelining

Rev.1.00 Jan. 10, 2008 Page 67 of 1658

REJ09B0261-0100

I1

I2

I3

(I1)

(ID)

ID

E1/S1 E2/s2 E3/s3

WB

I3

I3

I3

(I2)

(I3)

I1

I2

ID

E1/S1 E2/S2 E3/S3

WB

I1

I2

ID

E1/S1 E2/S2 E3/S3

WB

I1

I2

ID

s1

s2

s3

WB

E2s2

ID

E3s3

ID

WB

ID

I1

I2

I3

ID

S1

S2

S3

WB

E1s1

E3s3

E2s2

E1s1

E1s1

E1s1

E1s1

E2s2

E2s2

E2s2

E2s2

E3s3

E3s3

E3s3

E3s3

WB

WB

WB

WB

E2s2 E3s3 WB

E2s2 E3s3 WB

E1s1

E1s1

I1

I2

I3

ID

S1

S2

S3

WB

E1s1

(I1)

(ID)

(I2)

(I3)

(I1)

(ID)

(I2)

(I3)

(I1)

(ID)

(I2)

(I3)

(I1)

(ID)

(I2)

(I3)

E2s2

E3s3

WB

E1s1

ID

ID

ID

ID

ID

ID

ID

WB

ID

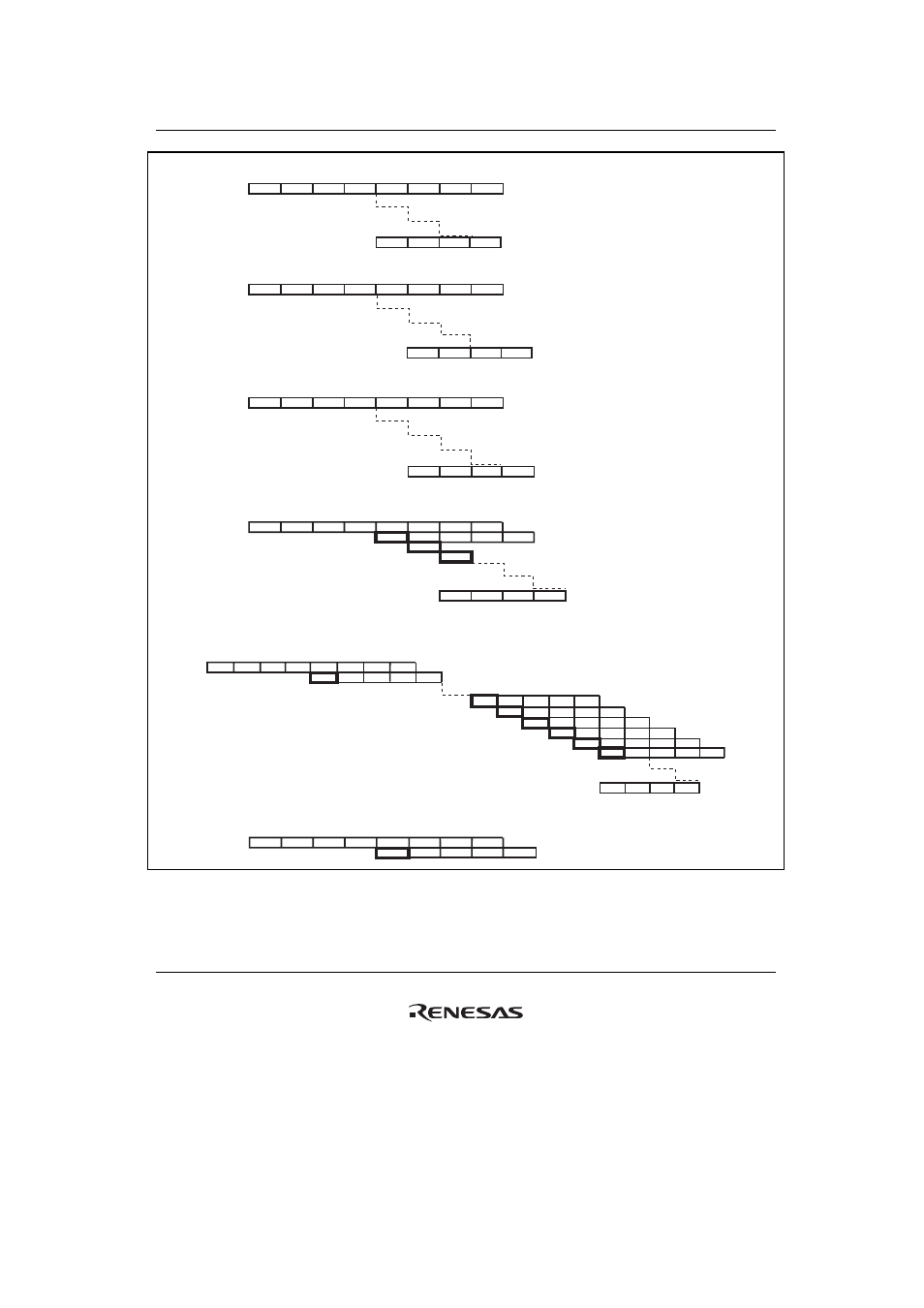

(1-1) BF, BF/S, BT, BT/S, BRA, BSR:1 issue cycle + 0 to 3 branch cycles

(1-2) JSR, JMP, BRAF, BSRF: 1 issue cycle + 4 branch cycles

(Branch destination instruction)

(1-3) RTS: 1 issue cycle + 0 to 4 branch cycles

(1-4) RTE: 4 issue cycles + 2 branch cycles

It is 15 cycles to the ID stage

in the first instruction of exception handler

(1-5) TRAPA: 8 issue cycles + 5 cycles + 2 branch cycle

It is not constant cycles to

the clock halted period.

(1-6) SLEEP: 2 issue cycles

(Branch destination instruction)

(Branch destination instruction)

(Branch destination instruction)

In branch instructions that are categorized

as (1-1), the number of branch cycles

may be reduced by prefetching.

Note:

Note:

Note:

Note: The number of branch cycles may be

0 by prefetching instruction.

Figure 4.2 Instruction Execution Patterns (1)