Renesas SH7781 User Manual

Page 1168

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1138 of 1658

REJ09B0261-0100

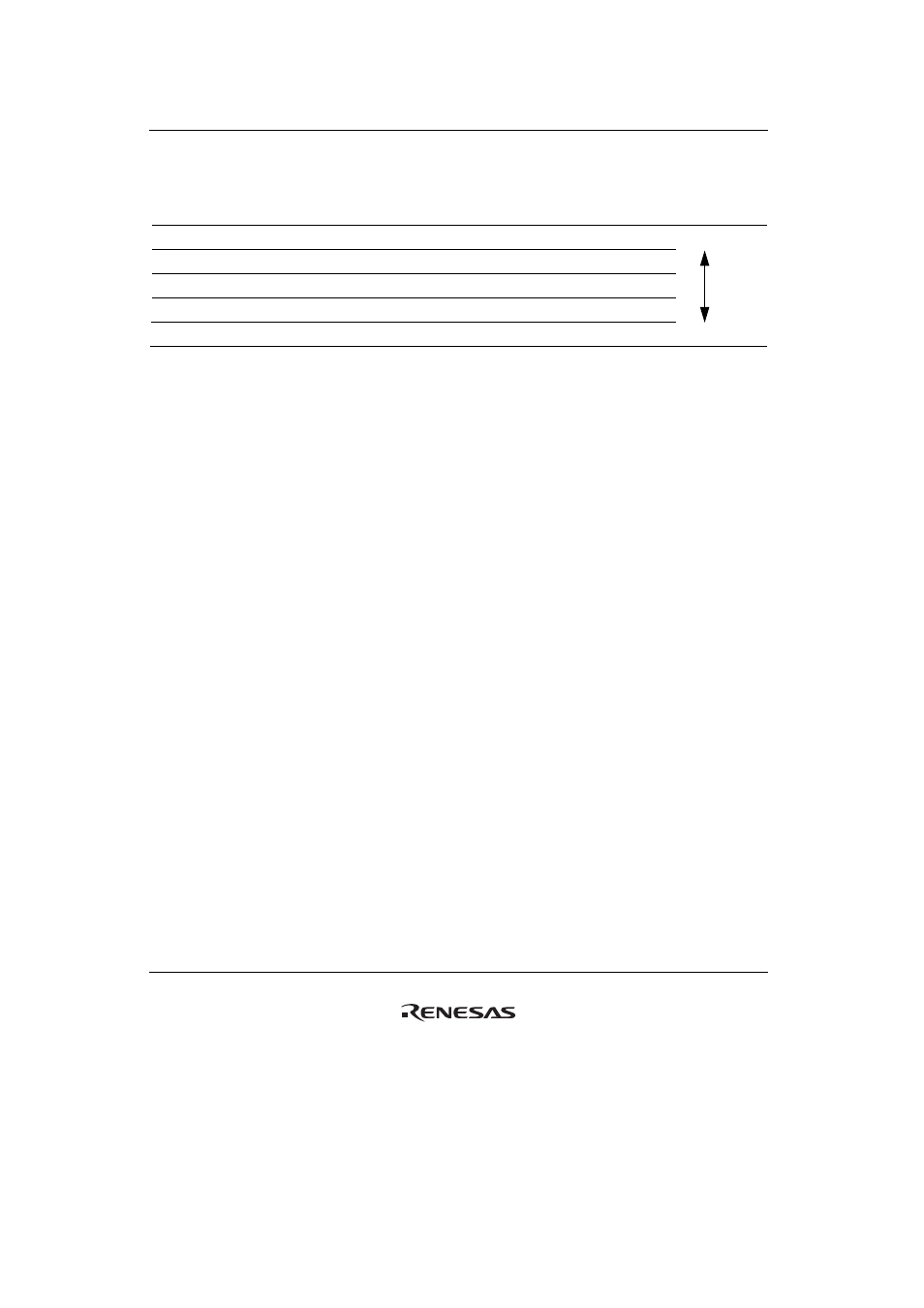

Table 22.12 Conditions to Issue Receive Request

RFWM2 to

RFWM0

Number of

Requested Stages*

Receive Request

Used Areas

000

1

Valid data is 1 stage or more

100

4

Valid data is 4 stages or more

101

8

Valid data is 8 stages or more

110

12

Valid data is 12 stages or more

Smallest

111

16

Valid data is 16 stages

Largest

Note: * The number of requested stages is the number of stages in transmit/receive FIFO.

The number of stages of the FIFO is always sixteen even if the data area or empty area exceeds the

FIFO size. Accordingly, an overflow error or underflow error occurs if data area or empty area

exceeds sixteen FIFO stages.

The FIFO transmit or receive request is canceled when the above condition is not satisfied even if

the FIFO is not empty or full.

(3)

Number of FIFOs

The number of FIFO stages used in transmission and reception is indicated by the following

register.

• Transmit FIFO: The number of empty FIFO stages is indicated by the TFUA4 to TFUA0 bits

in SIFCTR.

• Receive FIFO: The number of valid data stages is indicated by the bits RFUA4 to RFUA0 bits

in SIFCTR.

The above indicates possible data numbers that can be transferred by the CPU or DMAC.