5 utlb data array (tlb compatible mode) – Renesas SH7781 User Manual

Page 226

7. Memory Management Unit (MMU)

Rev.1.00 Jan. 10, 2008 Page 196 of 1658

REJ09B0261-0100

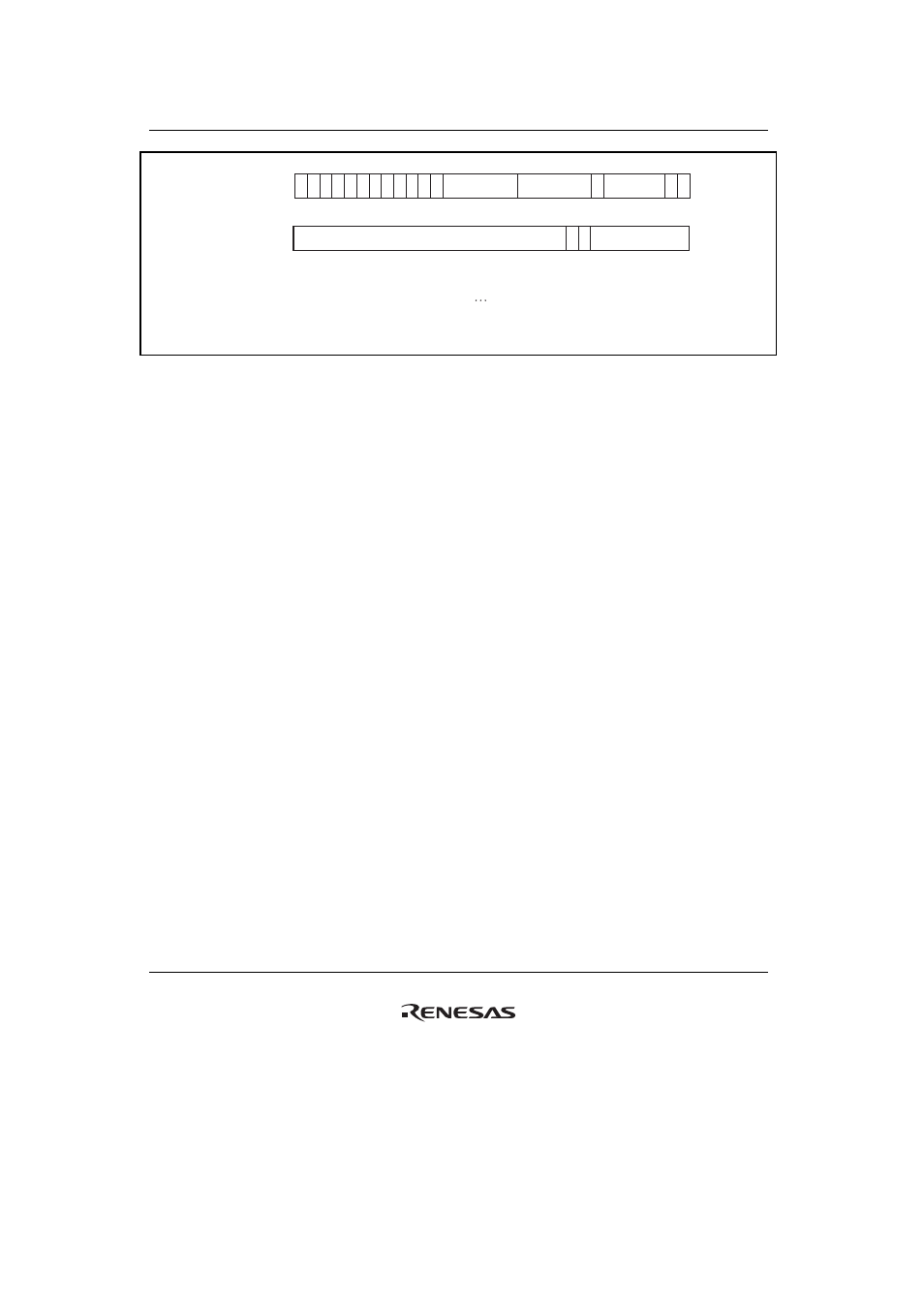

Address field

Data field

VPN:

V:

E:

D:

*:

Virtual page number

Validity bit

Entry

Dirty bit

Don't care

ASID:

A:

:

Address space identifier

Association bit

Reserved bits (write value should be 0

and read value is undefined )

31

0

V

D

10 9 8 7

ASID

VPN

A

8 7

2 1

31

0

1 1 1 1 0 1 1 0 0 0 0 0

0 0

E

19

20

14 13

* * * * *

* * * * *

*

Figure 7.22 Memory-Mapped UTLB Address Array

7.7.5

UTLB Data Array (TLB Compatible Mode)

The UTLB data array is allocated to addresses H'F700 0000 to H'F70F FFFF in the P4 area. A

data array access requires a 32-bit address field specification (when reading or writing) and a 32-

bit data field specification (when writing). Information for selecting the entry to be accessed is

specified in the address field, and PPN, V, SZ, PR, C, D, SH, and WT to be written to data array

are specified in the data field.

In the address field, bits [31:20] have the value H'F70 indicating UTLB data array and the entry is

specified by bits [13:8].

In the data field, bits [28:10] indicate PPN, bit [8] indicates V, bits [7] and [4] indicate SZ, bits

[6:5] indicate PR, bit [3] indicates C, bit [2] indicates D, bit [1] indicates SH, and bit [0] indicates

WT.

The following two kinds of operation can be used on UTLB data array:

1. UTLB data array read

PPN, V, SZ, PR, C, D, SH, and WT are read into the data field from the UTLB entry

corresponding to the entry set in the address field.

2. UTLB data array write

PPN, V, SZ, PR, C, D, SH, and WT specified in the data field are written to the UTLB entry

corresponding to the entry set in the address field.