3 master access – Renesas SH7781 User Manual

Page 662

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 632 of 1658

REJ09B0261-0100

13.4.3

Master Access

This section describes how software controls the PCI when the PCIC is a bus master. This section

describes the cases where the PCIC is used in both host mode and normal mode.

(1)

Address Map

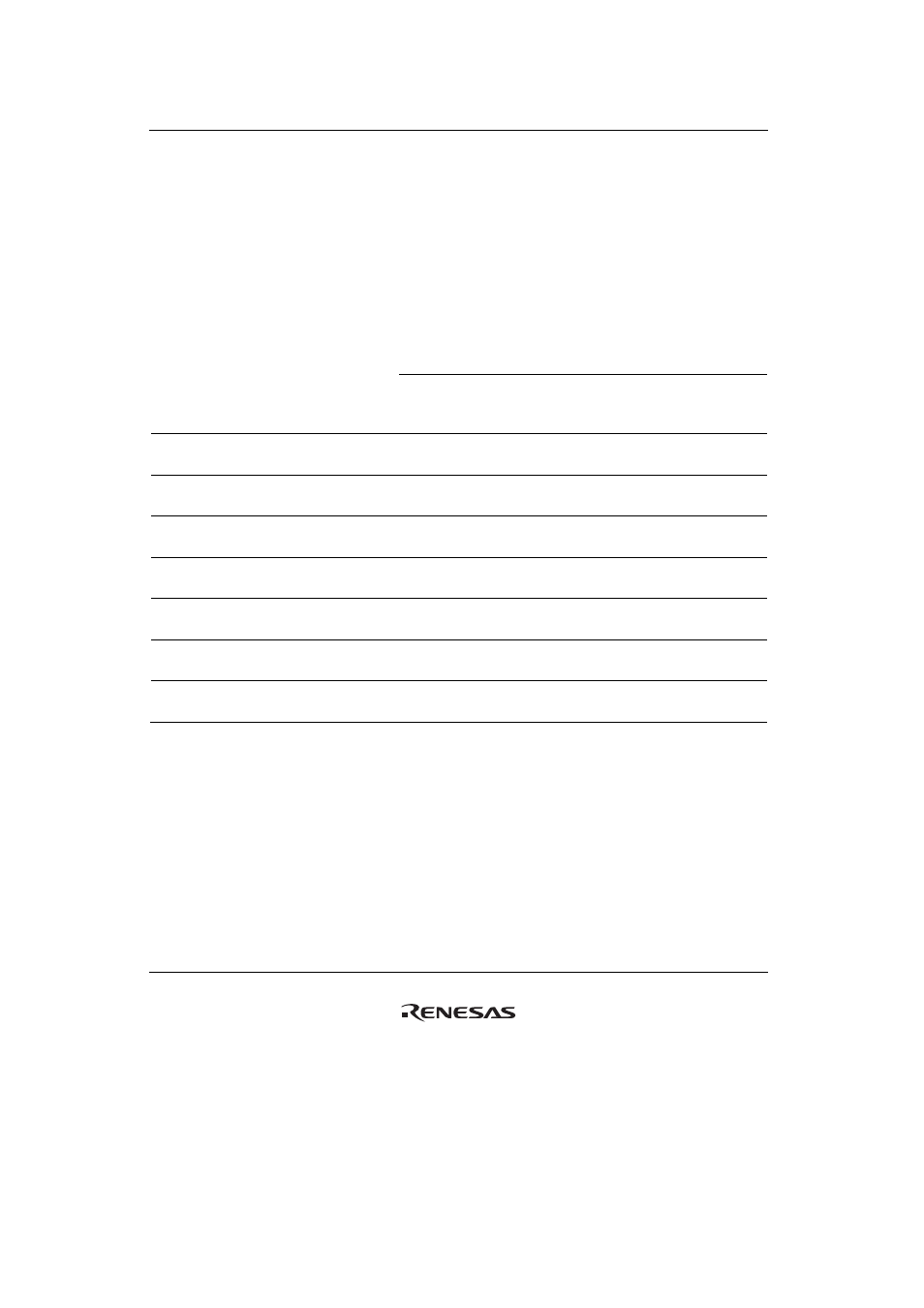

Table 13.5 shows the PCIC address map.

Table 13.5 PCIC Address Map

Address

Memory Space

29-Bit Address

Mode*

1

32-Bit Address

Extended Mode*

1

Physical

Address

Size

PCI memory space1

(Area 4: PCI selected*

2

)

H'1000 0000 to

H'13FF FFFF

H'1000 0000 to

H'13FF FFFF

64 Mbytes

PCI memory space 2

(Only 32-bit address extended mode*

1

)

—

H'C000 0000 to

H'DFFF FFFF

512 Mbytes

PCI memory space 0

H'FD00 0000 to

H'FDFF FFFF

H'FD00 0000 to

H'FDFF FFFF

16 Mbytes

Control register space

H'FE00 0000 to

H'FE03 FFFF

H'FE00 0000 to

H'FE03 FFFF

256 Kbytes

PCIC internal register

H'FE04 0000 to

H'FE07 FFFF

H'FE04 0000 to

H'FE07 FFFF

256 Kbytes

Reserved

H'FE08 0000 to

H'FE1F FFFF

H'FE08 0000 to

H'FE1F FFFF

1.5 Mbytes

PCI I/O space

H'FE20 0000 to

H'FE3F FFFF

H'FE20 0000 to

H'FE3F FFFF

2 Mbytes

Notes: 1. Please see MMU about 29/32bit address mode

2. Please see LBSC.

The PCIC has four types of address space (six types, physically). They are PCI memory (three

types), the control register space, PCIC internal control register (PCI configuration registers and

PCI local registers) spaces, and I/O space.