Table 17.1 states of power-down modes – Renesas SH7781 User Manual

Page 812

17. Power-Down Mode

Rev.1.00 Jan. 10, 2008 Page 782 of 1658

REJ09B0261-0100

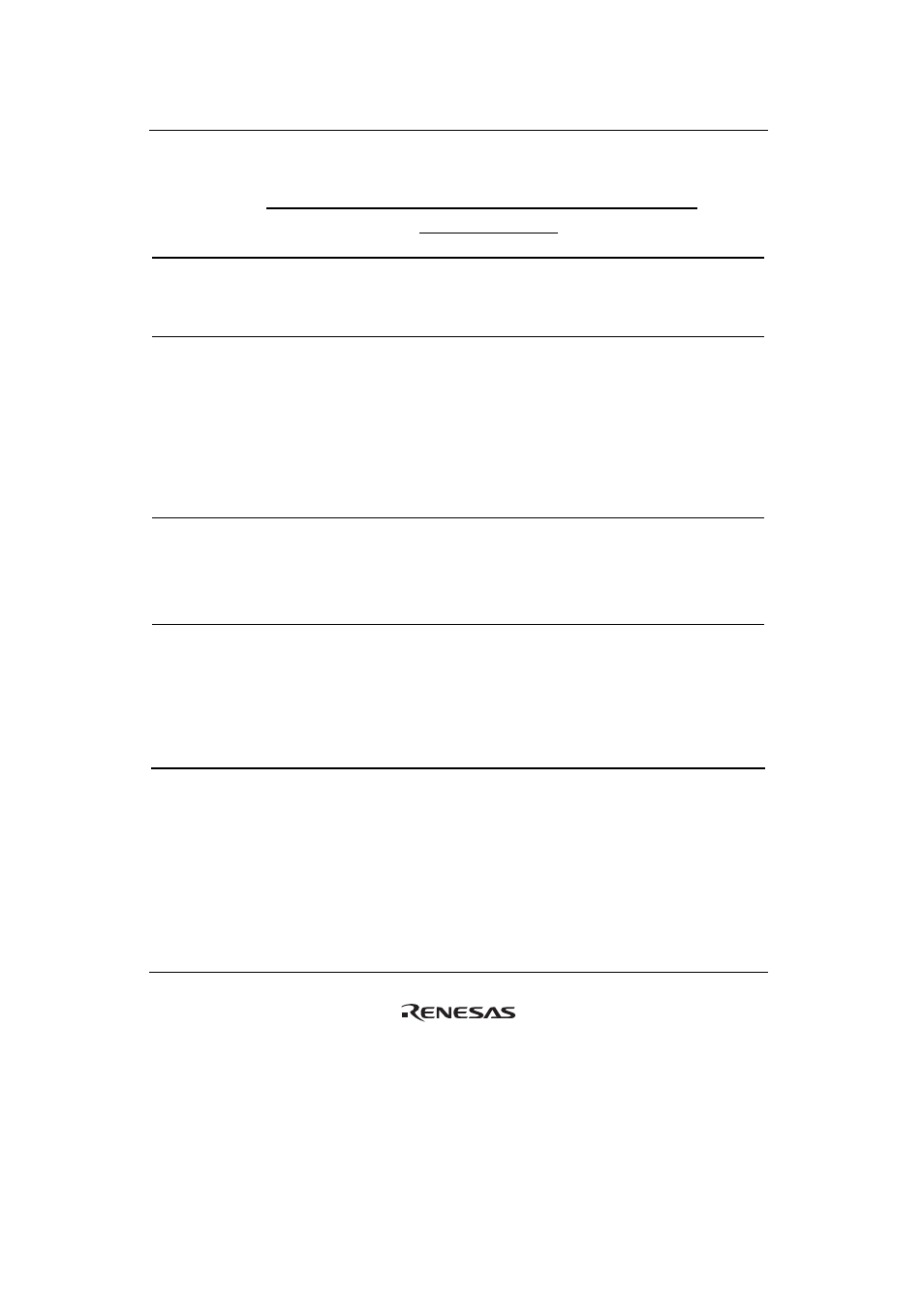

Table 17.1 States of Power-Down Modes

State

On-Chip Peripheral Module

Power-

Down

Mode

Conditions of

Transition

CPG CPU

On-Chip

Memory

DMAC GDTA Others Pin DDR2-SDRAM

Releasing

Methods

Sleep

mode

SLEEP

instruction

executed (see

section 17.4)

Operate Stopped

(contents

of registers

retained)

Retained Operate Operate Operate Operation

retained

Auto-refresh or

self-refresh*

3

1. Interrupt

2. Power-on

reset

3. Manual

reset

Deep

sleep

mode

Corresponding

bit in MSTPCR

set to 1 (see

section 17.3.2)

Operate Stopped

(contents

of registers

retained)

Retained Stopped

(contents

of

registers

retained)

Stopped

(contents

of

registers

retained)

Operate

(DU,

TMU,

SCIF,

SIOF,

HSPI,

MMCIF,

HAC,

SSI,

FLCTL,

and UBC

are

stopped

*

1

)

Operation

retained

Self-refresh 1.

Interrupt

2. Power-on

reset

3. Manual

reset

Module

standby

function

Clear the

corresponding

bits in

MSTPCR0 and

MSTPCR1 to 0

(see sections

17.3.2 and

17.3.3)

Operate Operate Retained Stopped

in six-

channel

units:

channels

0 to 5 and

channels

6 to 11.

Stopped Specified

modules

stopped

Operation

retained

Auto-refresh or

self-refresh

Clear the

corresponding

bits in

MSTPCR0 and

MSTPCR1 to 0

(see sections

17.3.2 and

17.3.3)

DDR2-

SDRAM

power

supply

backup *

2

See section

17.7

Stopped Stopped Undefined

Stopped

Stopped

Stopped

Undefined

except for the

1.8-V power

supply

interface

(When the

MBKPRST is

low level input,

the MCKE is

high level

output)

Self-refresh Power-on

reset

Notes: 1. The TMU, SCIF, SIOF, HSPI, MMCIF, HAC, SSI, FLCTL and UBC should be in module

stop state by using the module standby function before execute the SLEEP instruction

to make transition to deep sleep mode. For detail, refer to section 17.5, Deep Sleep

Mode.

2. Power supplies (1.1 V, 3.3 V) except the 1.8 V power supply are stopped in DDR2-

SDRAM power supply backup mode. Therefore, all circuitry other than the pad of DDR2

interface are stopped, including DDR2 interface control unit, and the contents of

registers are not retained.

3. For details on auto-refresh and self-refresh operation, see section 12, DDR2-SDRAM

Interface (DBSC2).