Renesas SH7781 User Manual

Page 1179

22. Serial I/O with FIFO (SIOF)

Rev.1.00 Jan. 10, 2008 Page 1149 of 1658

REJ09B0261-0100

(6)

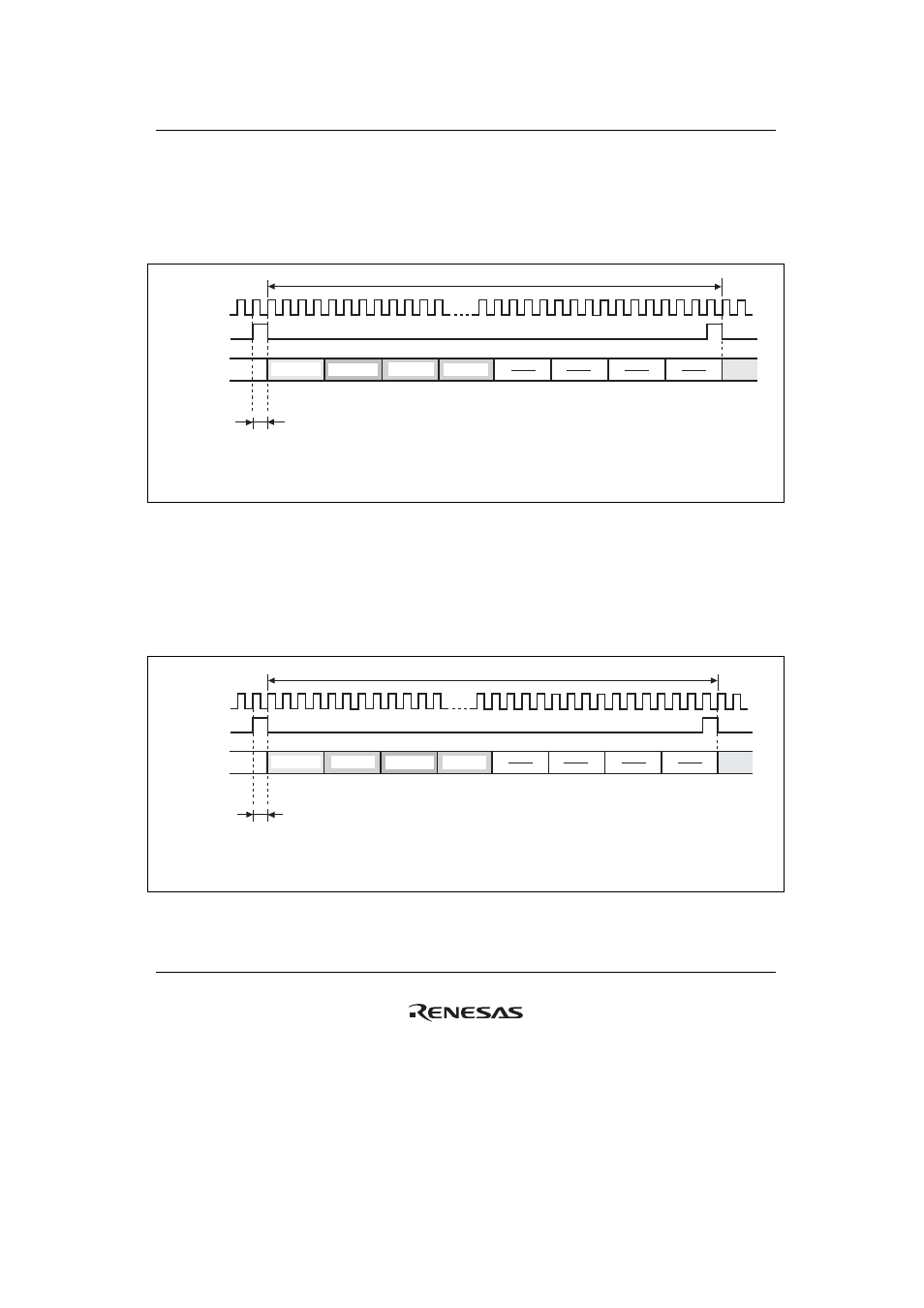

16-bit Stereo Data (3)

Synchronous pulse method, falling edge sampling, slot No.0 used for left-channel data, slot No.1

used for right-channel data, slot No.2 used for control channel 0 data, slot No.3 used for control

channel 1 data, and frame length = 128 bits

TRMD[1:0] = 00 or 10,

TDLE = 1,

RDLE = 1,

CD0E = 1,

REDG = 0,

TDLA[3:0] = 0000,

RDLA[3:0] = 0000,

CD0A[3:0] = 0010,

FL[3:0] = 1110 (frame length: 128 bits),

TDRE = 1,

RDRE = 1,

CD1E = 1,

TDRA[3:0] = 0001,

RDRA[3:0] = 0001,

CD1A[3:0] = 0011

Slot No.0

Slot No.1

Slot No.2

Slot No.3

Slot No.4

Slot No.5

Slot No.6

Slot No.7

Specifications:

1 frame

1 bit delay

SYNCDL = 1

SIOF

_SCK

SIOF

_RXD

SIOF_TXD

SIOF

_SYNC

L-channel

data

R-channel

data

Control

channel 0

Control

channel 1

Figure 22.18 Transmit and Receive Timing (16-Bit Stereo Data (3))

(7)

16-bit Stereo Data (4)

Synchronous pulse method, falling edge sampling, slot No.0 used for left-channel data, slot No.2

used for right-channel data, slot No.1 used for control channel 0 data, slot No.3 used for control

channel 1 data, and frame length = 128 bits

TRMD[1:0] = 00 or 10,

TDLE = 1,

RDLE = 1,

CD0E = 1,

REDG = 1,

TDLA[3:0] = 0000,

RDLA[3:0] = 0000,

CD0A[3:0] = 0001,

FL[3:0] = 1110 (frame length: 128 bits)

TDRE = 1,

RDRE = 1,

CD1E = 1,

TDRA[3:0] = 0010,

RDRA[3:0] = 0010,

CD1A[3:0] = 0011

Slot No.0

Slot No.1

Slot No.2

Slot No.3

Slot No.4

Slot No.5

Slot No.6

Slot No.7

Specifications:

1 frame

1 bit delay

SYNCDL = 1

SIOF_SCK

SIOF_RXD

SIOF_TXD

SIOF_SYNC

L-channel

data

Control

channel 0

Control

channel 1

R-channel

data

Figure 22.19 Transmit and Receive Timing (16-Bit Stereo Data (4))