Renesas SH7781 User Manual

Page 568

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 538 of 1658

REJ09B0261-0100

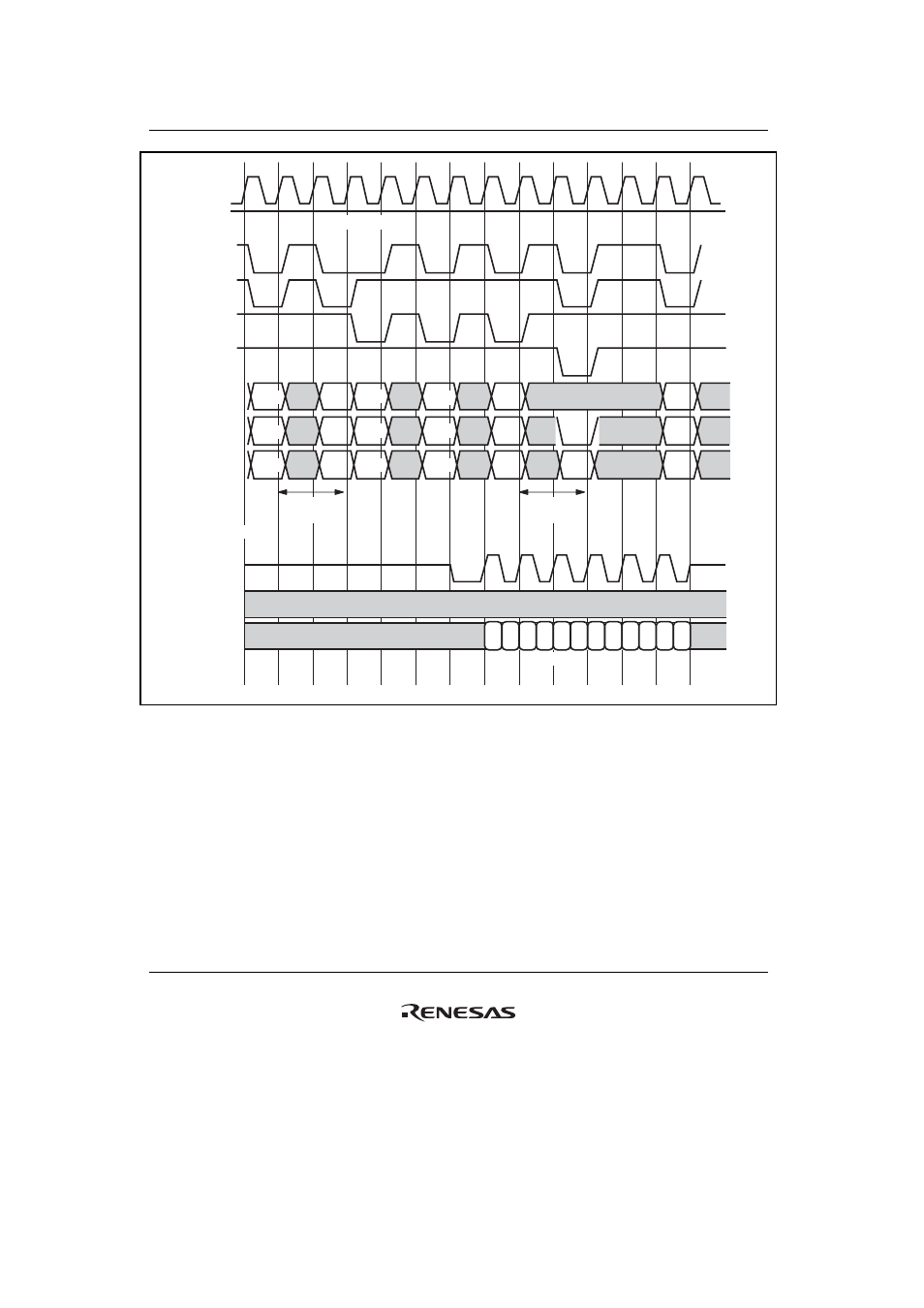

MCK0,

MCK1

MA[14:11]

MA[9:0]

MBA[2:0]

MCKE

MCS

MRAS

MCAS

MWE

MA[10]

ACT

bank A

READ

bank A

Invalid

Invalid

Invalid

Invalid

Invalid

Invalid

MDQS[3:0]

MDQ[31:0]

MDM[3:0]

Invalid

Invalid

Invalid

Valid

PRE

bank C

Valid

Valid

Valid

ACT

bank B

READ

bank B

READ

bank C

Invalid

Invalid

Invalid

Invalid

Invalid

Invalid

Valid

Valid

Valid

SDRAM

command

Valid

Valid

Valid

ACT

bank C

Invalid

Invalid

Invalid

Invalid

Invalid

tRTP

= 2 cycles

Read data

tRRD

= 2 cycles

Example of CL = 3

Valid

Valid

Valid

Valid

Valid

Valid

Valid

Valid

Valid

High level

Figure 12.15 tRRD and tRTP

Figure 12.15 shows a case in which the pages for both of banks A and B are closed, the page for

bank C is open, and a page hit has occurred. When the tRRD time constraint has been satisfied

starting from issue of the ACT command for bank A, the ACT command for bank B is issued.

Because time tRCD has elapsed from the issue of the ACT command for bank A, a READ

command can be used. The READ command has a burst length of 4, so after two cycles a READ

command for bank B can be issued. A further two cycles later, a READ command for bank C can

be issued. However, the next request is access for which bank C must be closed, and so after the

elapse of time tRTP a PRE command is issued.