Renesas SH7781 User Manual

Page 68

2. Programming Model

Rev.1.00 Jan. 10, 2008 Page 38 of 1658

REJ09B0261-0100

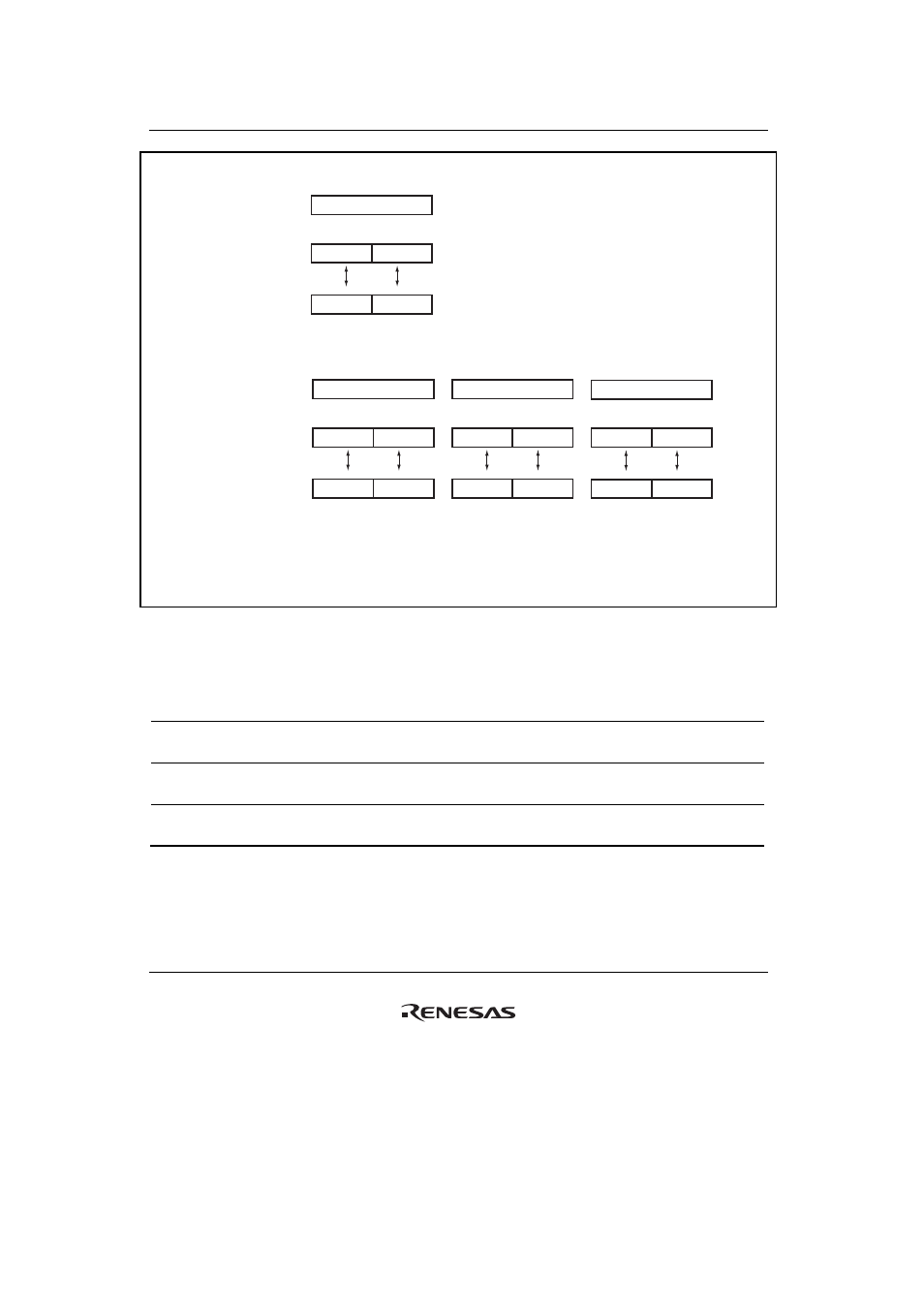

DR (2i)

FR (2i)

FR (2i+1)

8n+4

8n+7

8n

8n+3

63

0

63 32 31 0

Floating-point register

Memory area

63

0

Floating-point register

Memory area

DR (2i)

FR (2i)

FR (2i+1)

4n

4m

4n+3

4m+3

63

0

63 32 31 0

DR (2i)

FR (2i+1)

FR (2i)

8n+4

8n+7

8n+3

8n

63

0

63 32 31 0

(1) SZ = 0

(2) SZ = 1, PR = 0

63

0

63

0

DR (2i)

FR (2i+1)

FR (2i)

8n

8n+3

8n+7

8n+4

63

0

63 32 31 0

(3) SZ = 1, PR = 1

63

0

*

1,

*

2

*

2

Notes: 1. In the case of SZ = 0 and PR = 0, DR register can not be used.

2. The bit-location of DR register is used for double precision format when PR = 1.

(In the case of (2), it is used when PR is changed from 0 to 1.)

Figure 2.5 Relationship between SZ bit and Endian

Table 2.2

Bit Allocation for FPU Exception Handling

Field Name

FPU

Error (E)

Invalid

Operation (V)

Division

by Zero (Z)

Overflow

(O)

Underflow

(U)

Inexact

(I)

Cause FPU

exception

cause field

Bit 17

Bit 16

Bit 15

Bit 14

Bit 13

Bit 12

Enable FPU

exception

enable field

None

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Flag

FPU exception flag

field

None

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

(5)

Floating-Point Communication Register (FPUL) (32 bits, Initial Value = Undefined)

Information is transferred between the FPU and CPU via FPUL.