1 clock and control signal timing – Renesas SH7781 User Manual

Page 1598

32. Electrical Characteristics

Rev.1.00 Jan. 10, 2008 Page 1568 of 1658

REJ09B0261-0100

32.3.1

Clock and Control Signal Timing

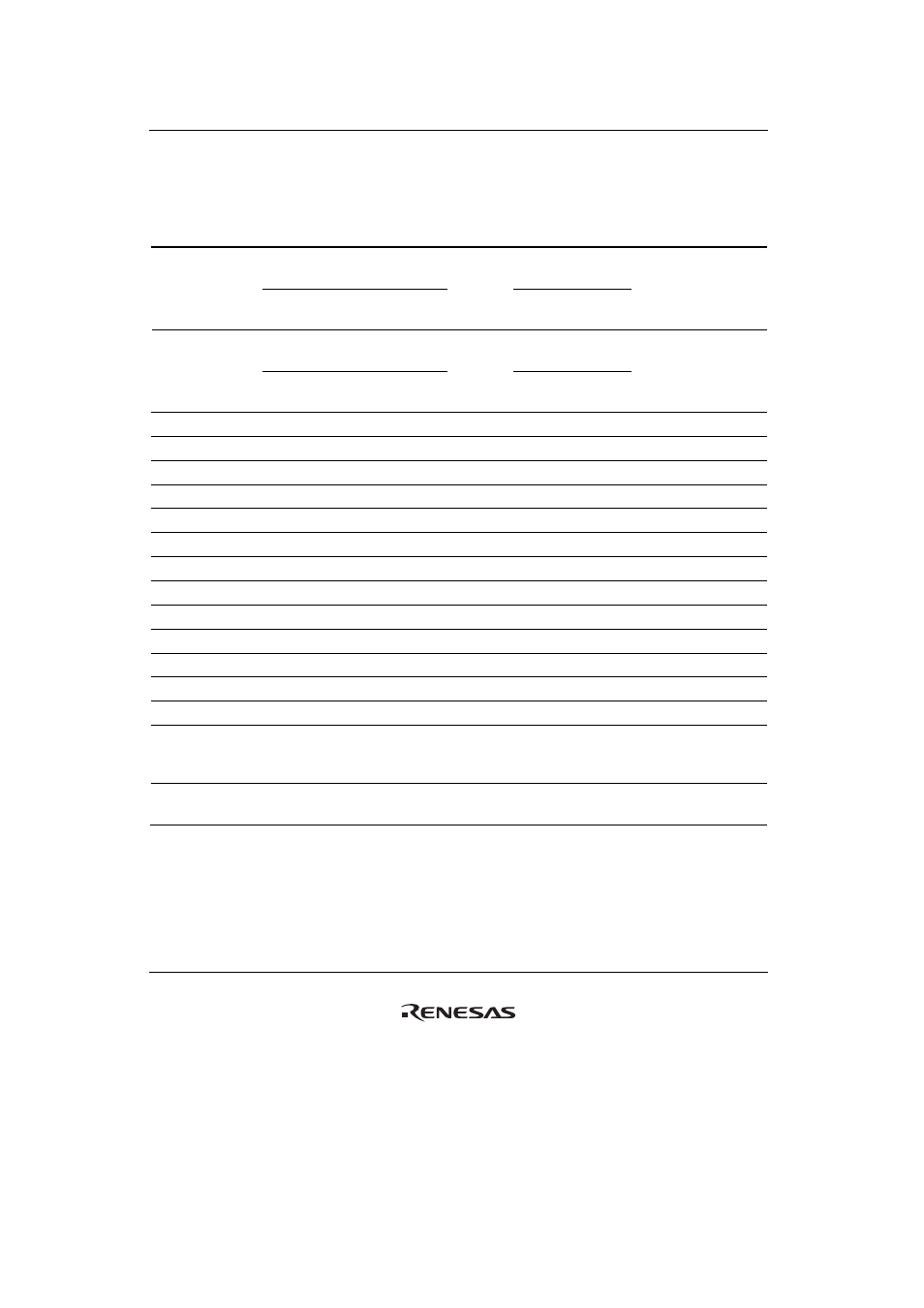

Table 32.6 Clock and Control Signal Timing

Item Symbol

Min.

Max.

Unit

Figure

Divider 1:

× 1, PLL1: × 72,

PLL2 in operation*

4

f

EX

12

17 MHz

EXTAL clock

input frequency

Divider 1:

× 1, PLL1: × 36,

PLL2 in operation*

6

23

34

Divider 1:

× 1, PLL1: × 72,

PLL2 in operation*

4

t

EXcyc

59 83 ns

32.1

EXTAL clock

input cycle time

Divider 1:

× 1, PLL1: × 36,

PLL2 in operation*

6

29

43

EXTAL clock input low pulse width

t

EXL

3.5

⎯ ns

32.1

EXTAL clock input high pulse width

t

EXH

3.5

⎯ ns

32.1

EXTAL clock input rise time

t

EXr

⎯ 4 ns

32.1

EXTAL clock input fall time

t

EXf

⎯ 4 ns

32.1

CLKOUT clock output (with use of PLL1/PLL2) f

OP

25

101

MHz

CLKOUT clock output cycle time

t

CKOcyc

10 1000 ns 32.2

CLKOUT clock output low pulse width

t

CKOL1

1

⎯ ns

32.2

CLKOUT clock output high pulse width

t

CKOH1

1

⎯ ns

32.2

CLKOUT clock output rise time

t

CKOr

⎯ 3 ns

32.2

CLKOUT clock output fall time

t

CKOf

⎯ 3 ns

32.2

CLKOUT clock output low pulse width

t

CKOL2

3

⎯ ns

32.3

CLKOUT clock output high pulse width

t

CKOH2

3

⎯ ns

32.3

Power-on oscillation settling time

t

OSC1

10

⎯ ms

32.4

Power-on oscillation settling time/mode

(MODE14, MODE10, MODE9, MODE4 to

MODE0) settling time

t

OSCMD

10

⎯ ms

32.4

MODE (MODE13 to MODE11, MODE8 to

MODE5) reset setup time

t

MDRS

3

⎯

t

cyc

32.6