Renesas SH7781 User Manual

Page 935

19. Display Unit (DU)

Rev.1.00 Jan. 10, 2008 Page 905 of 1658

REJ09B0261-0100

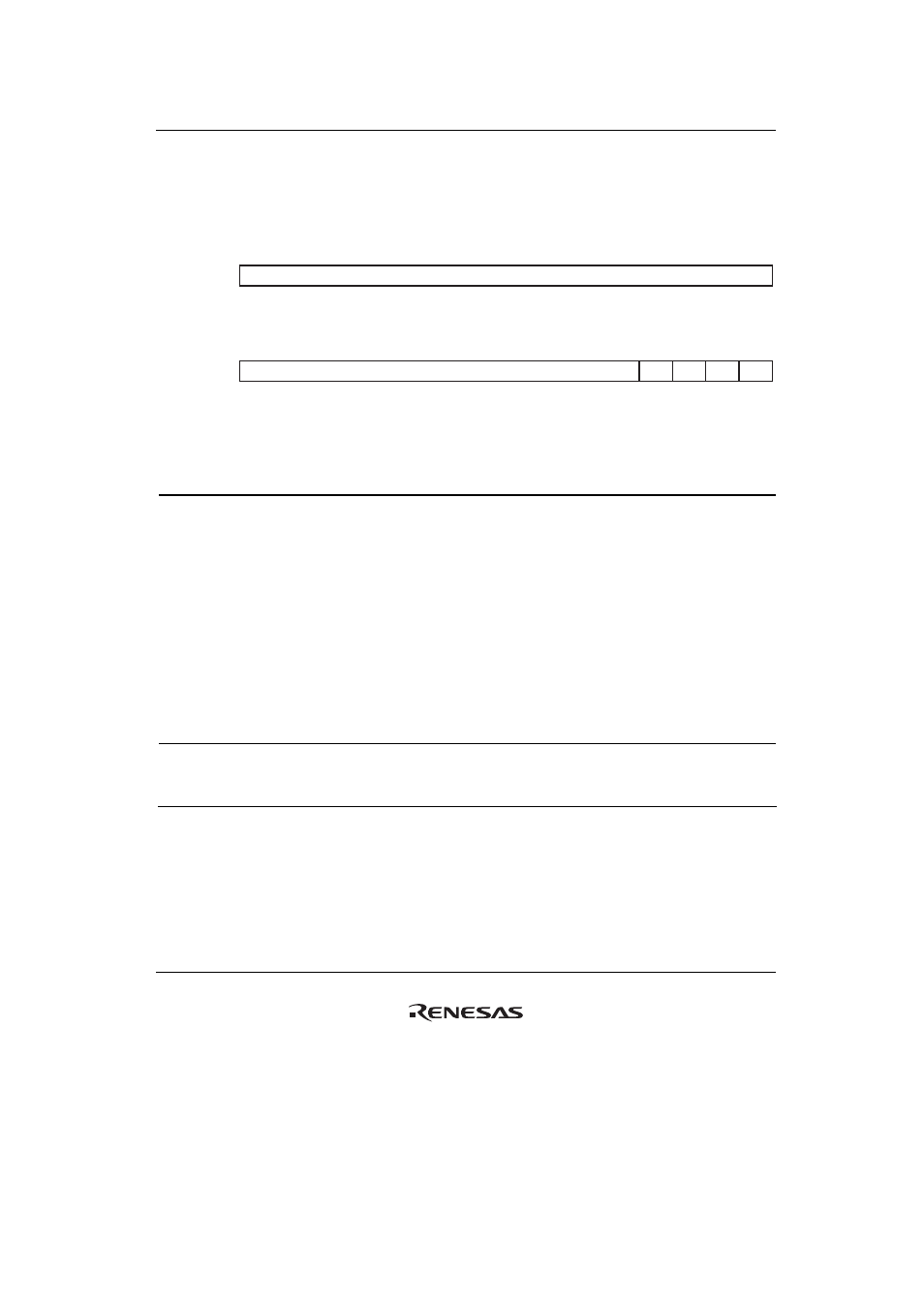

19.3.38

Plane n Display Area Start Address 0 Register (PnDSA0R) (n

= 1 to 6)

The plane n display area start address 0 registers (PnDSA0R, n = 1 to 6) set the memory area in

frame buffer 0 for plane n. The value is retained during power-on reset and manual reset.

R/W:

Internal update:

R/W:

Internal update:

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

Bit:

Initial value:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

PnDSA0

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

O

O

O

O

O

O

O

O

O

O

O

O

0

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

PnDSA0

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

Bit:

Initial value:

Bit Bit

Name

Initial

Value R/W

Internal

Update Description

31 to 4

PnDSA0 Undefined R/W

Yes

Plane n Display Area Start Address 0

To enable the 31 to 29 bits, the DSAE bit in

DEFR should be set to 1.

In the initial state the bits are not enabled, and

are fixed at 0.

When the buffer mode for plane n is manual

display change mode or auto display change

mode, the buffer is used as frame buffer 0.

Note: In 32-bit address extended mode, when

the 31 to 29 bits in this register are

disabled, of the lower 29 bits in a specified

32-bit physical address, a 25-bit address

(A28 to A4) is specified in the 28 to 4 bits.

3 to 0

⎯ All

0

R

⎯ Reserved

These bits are always read as 0. The write value

should always be 0.