3 register descriptions – Renesas SH7781 User Manual

Page 1004

20. Graphics Data Translation Accelerator (GDTA)

Rev.1.00 Jan. 10, 2008 Page 974 of 1658

REJ09B0261-0100

20.3

Register Descriptions

Table 20.1 to 20.3 show the register configuration of the GDTA. Table 20.4 to 20.6 show the

register states in each processing mode.

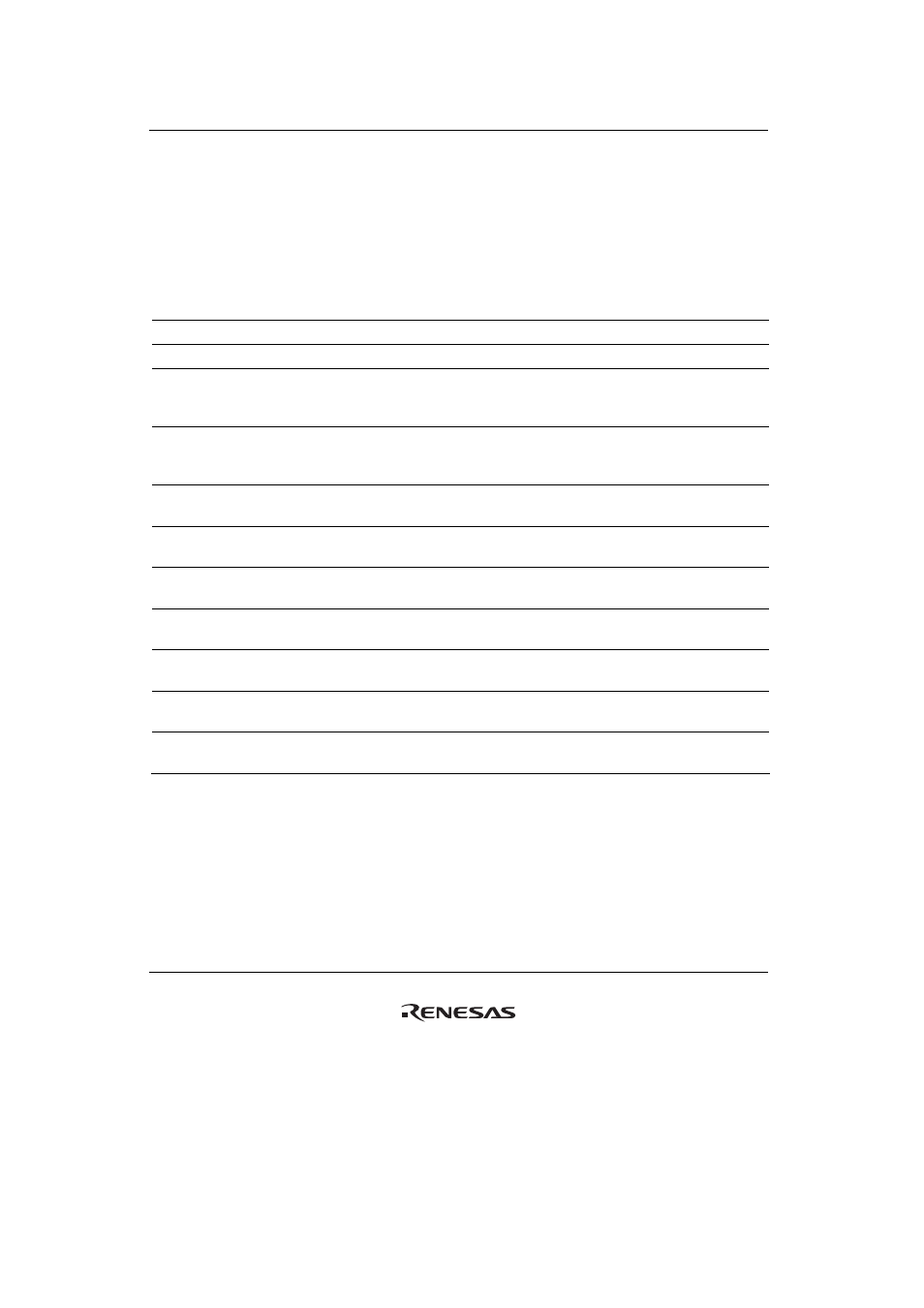

Table 20.1 GDTA Register Configuration (GDTA Common Registers)

Name Abbreviation

R/W

P4

Address

Area 7

Address

Access

Size

Sync

Clock

GA mask register

GACMR

R/W

H'FE40 000C H'1E40 000C 32

GAck

GA enable register

GACER

R/W

H'FE40 0010 H'1E40 0010

32

GAck

GA processing end

interrupt source

indicating register

GACISR

R

H'FE40 0014 H'1E40 0014

32

GAck

GA processing end

interrupt source

indication clear register

GACICR

W

H'FE40 0018 H'1E40 0018

32

GAck

GA interrupt enable

register

GACIER

R/W

H'FE40 001C H'1E40 001C 32

GAck

GA CL output data

alignment register

DWCL_CTL

R/W

H'FE40 3000 H'1E40 3000

32

GAck

GA CL input data

alignment register

DRCL_CTL

R/W

H'FE40 3200 H'1E40 3200

32

GAck

GA MC input data

alignment register

DRMC_CTL

R/W

H'FE40 3400 H'1E40 3400

32

GAck

GA MC output data

alignment register

DWMC_CTL

R/W

H'FE40 3600 H'1E40 3600

32

GAck

GA buffer RAM 0 data

alignment register

DCP_CTL

R/W

H'FE40 3800 H'1E40 3800

32

GAck

GA buffer RAM 1 data

alignment register

DID_CTL

R/W

H'FE40 3A00 H'1E40 3A00 32

GAck