Figure 14.4 data flow of dual address mode – Renesas SH7781 User Manual

Page 741

14. Direct Memory Access Controller (DMAC)

Rev.1.00 Jan. 10, 2008 Page 711 of 1658

REJ09B0261-0100

(1)

Dual Address Mode

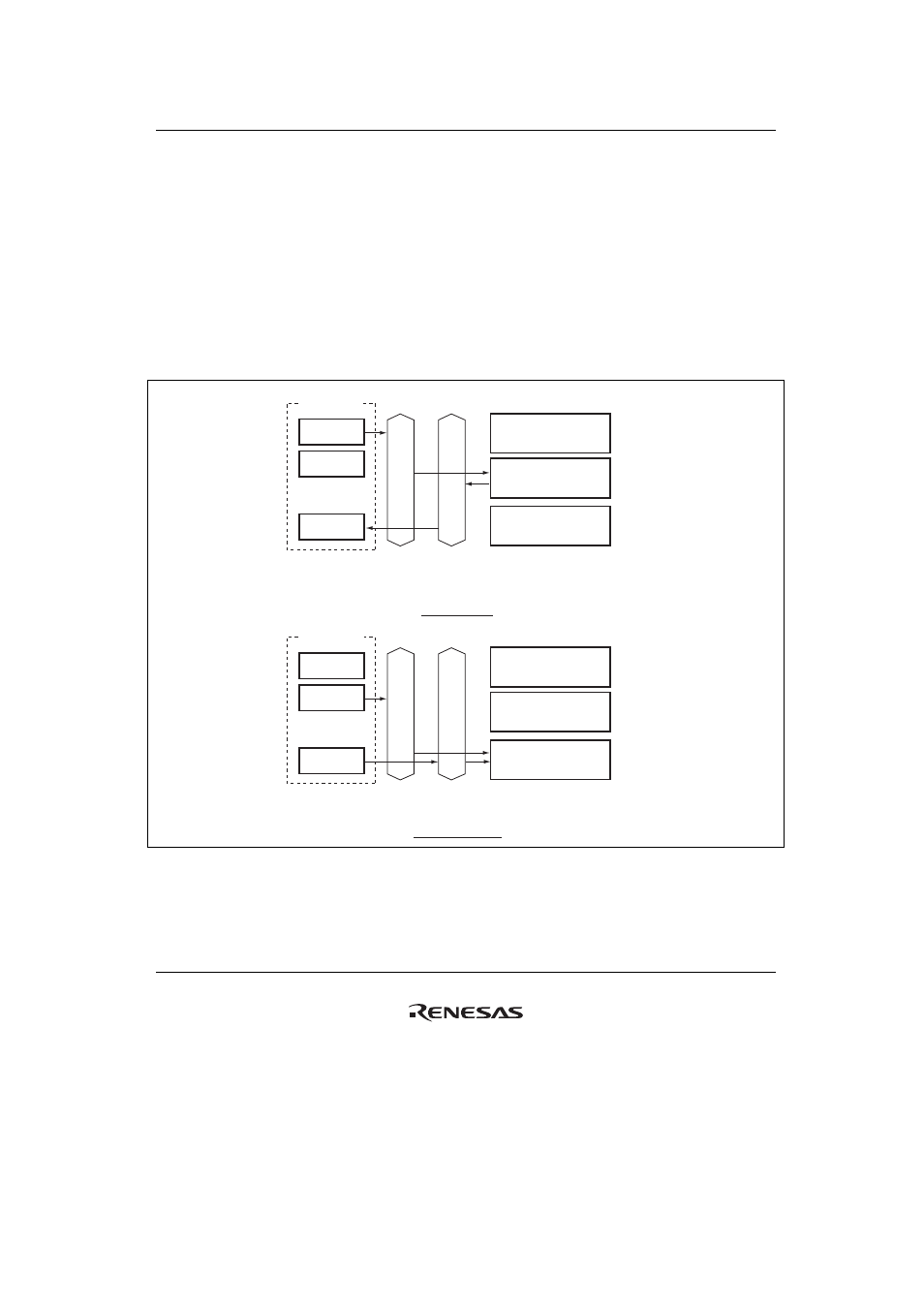

In dual address mode, both the transfer source and transfer destination are accessed by address.

The source and destination can be specified externally or internally. Data is read from the transfer

source in a data read cycle and written to the transfer destination in a data write cycle, and two bus

cycles are required to execute DMA transfer. At this time, transfer data is temporarily stored in the

DMAC. In the transfer between external memories shown in figure 14.4, data is read from an

external memory to the DMAC in a data read cycle, and then the data is written to the other

external memory in a write cycle.

Figure 14.5 shows the DMA transfer timing in dual address mode.

Data buffer

Address b

us

Data b

us

Address b

us

Data b

us

Memory

Transfer source

module

Transfer destination

module

Memory

Transfer source

module

Transfer destination

module

SAR

DAR

Data buffer

SAR

DAR

The SAR value is an address, data is read from the transfer source module,

and the data is temporarily stored in the DMAC.

First bus cycle

Second bus cycle

The DAR value is an address and the value stored in the data buffer in the

DMAC is written to the transfer destination module.

DMAC

DMAC

Figure 14.4 Data Flow of Dual Address Mode