Renesas SH7781 User Manual

Page 1006

20. Graphics Data Translation Accelerator (GDTA)

Rev.1.00 Jan. 10, 2008 Page 976 of 1658

REJ09B0261-0100

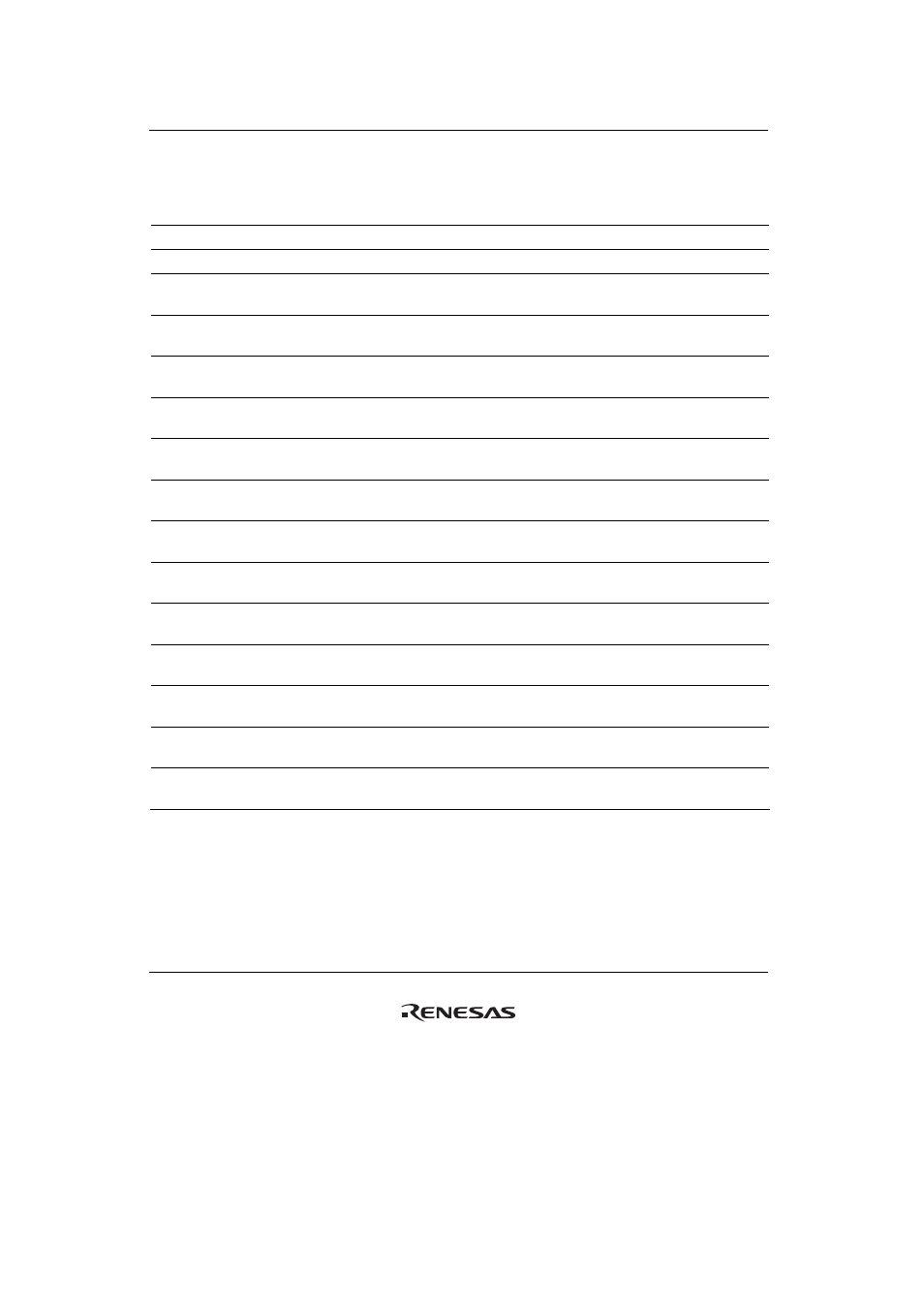

Table 20.3 GDTA Register Configuration (MC Block)

Name Abbreviation

R/W

P4

Address

Area 7

Address

Access

Size

Sync

Clock

MC command FIFO

MCCF

W

H'FE40 2000 H'1E40 2000

32

GAck

MC status register

MCSR

R

H'FE40 2004 H'1E40 2004

32

GAck

MC frame width setting

register

MCWR

R/W

H'FE40 2008 H'1E40 2008

32

GAck

MC frame height setting

register

MCHR

R/W

H'FE40 200C H'1E40 200C 32

GAck

MC Y padding size

setting register

MCYPR

R/W

H'FE40 2010 H'1E40 2010

32

GAck

MC UV padding size

setting register

MCUVPR

R/W

H'FE40 2014 H'1E40 2014

32

GAck

MC output frame Y

pointer register

MCOYPR

R/W

H'FE40 2018 H'1E40 2018

32

GAck

MC output frame U

pointer register

MCOUPR

R/W

H'FE40 201C H'1E40 201C 32

GAck

MC output frame V

pointer register

MCOVPR

R/W

H'FE40 2020 H'1E40 2020

32

GAck

MC past frame Y pointer

register

MCPYPR

R/W

H'FE40 2024 H'1E40 2024

32

GAck

MC past frame U pointer

register

MCPUPR

R/W

H'FE40 2028 H'1E40 2028

32

GAck

MC past frame V pointer

register

MCPVPR

R/W

H'FE40 202C H'1E40 202C 32

GAck

MC future frame Y

pointer register

MCFYPR

R/W

H'FE40 2030 H'1E40 2030

32

GAck

MC future frame U

pointer register

MCFUPR

R/W

H'FE40 2034 H'1E40 2034

32

GAck

MC future frame V

pointer register

MCFVPR

R/W

H'FE40 2038 H'1E40 2038

32

GAck