Renesas SH7781 User Manual

Page 589

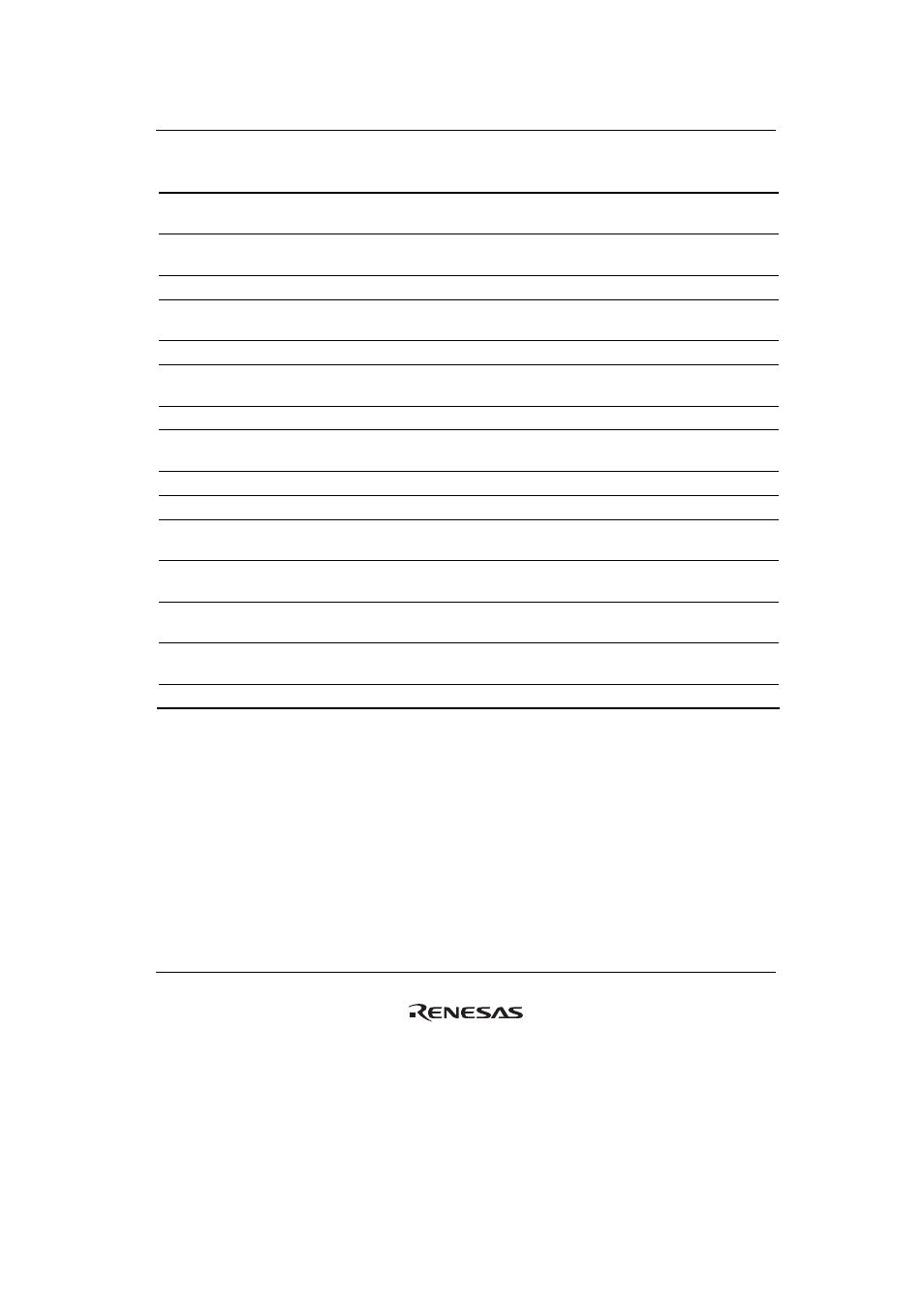

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 559 of 1658

REJ09B0261-0100

Name Abbreviation

SH*

1

R/W

PCI*

2

R/W P4

address

Area 7 address

Sync

Clock

Access

Size*

3

PCI power management

interrupt register

PCIPINT R/WC

—

H'FE04

01CC

H'1E04 01CC

PCIclk

32/16/8

PCI power management

interrupt mask register

PCIPINTM R/W

— H'FE04

01D0

H'1E04 01D0

PCIclk

32/16/8

PCI memory bank register 0

PCIMBR0

R/W

—

H'FE04 01E0

H'1E04 01E0

PCIclk

32/16/8

PCI memory bank mask

register 0

PCIMBMR0 R/W — H'FE04

01E4

H'1E04 01E4

PCIclk

32/16/8

PCI memory bank register 1

PCIMBR1

R/W

—

H'FE04 01E8

H'1E04 01E8

PCIclk

32/16/8

PCI memory bank mask

register 1

PCIMBMR1

R/W

—

H'FE04 01EC H'1E04 01EC

PCIclk

32/16/8

PCI memory bank register 2

PCIMBR2

R/W

—

H'FE04 01F0

H'1E04 01F0

PCIclk

32/16/8

PCI memory bank mask

register 2

PCIMBMR2 R/W — H'FE04

01F4

H'1E04 01F4

PCIclk

32/16/8

PCI I/O bank register

PCIIOBR

R/W

—

H'FE04 01F8

H'1E04 01F8

PCIclk

32/16/8

PCI I/O bank master register

PCIIOBMR

R/W

—

H'FE04 01FC H'1E04 01FC

PCIclk

32/16/8

PCI cache snoop control

register 0

PCICSCR0

R/W

—

H'FE04 0210

H'1E04 0210

PCIclk

32/16/8

PCI cache snoop control

register 1

PCICSCR1

R/W

—

H'FE04 0214

H'1E04 0214

PCIclk

32/16/8

PCI cache snoop address

register 0

PCICSAR0 R/W

— H'FE04

0218

H'1E04 0218

PCIclk

32/16/8

PCI cache snoop address

register 1

PCICSAR1 R/W

— H'FE04

021C

H'1E04 021C

PCIclk

32/16/8

PCI PIO data register

PCIPDR

R/W

—

H'FE04 0220

H'1E04 0220

PCIclk

32/16/8

Notes: 1. SH: SuperHyway bus (internal bus)

PCI: PCI local bus

WC in R/W column: Write clear (Cleared by writing 1; writing 0 has no effect.)

⎯: Access is prohibited.

2. PIO: Programmed I/O.

3. It It is possible to access multiple registers at once by using an access size exceeding

the register size.