4 pin arrangement, Pkg top view – Renesas SH7781 User Manual

Page 52

1. Overview

Rev.1.00 Jan. 10, 2008 Page 22 of 1658

REJ09B0261-0100

1.4

Pin Arrangement

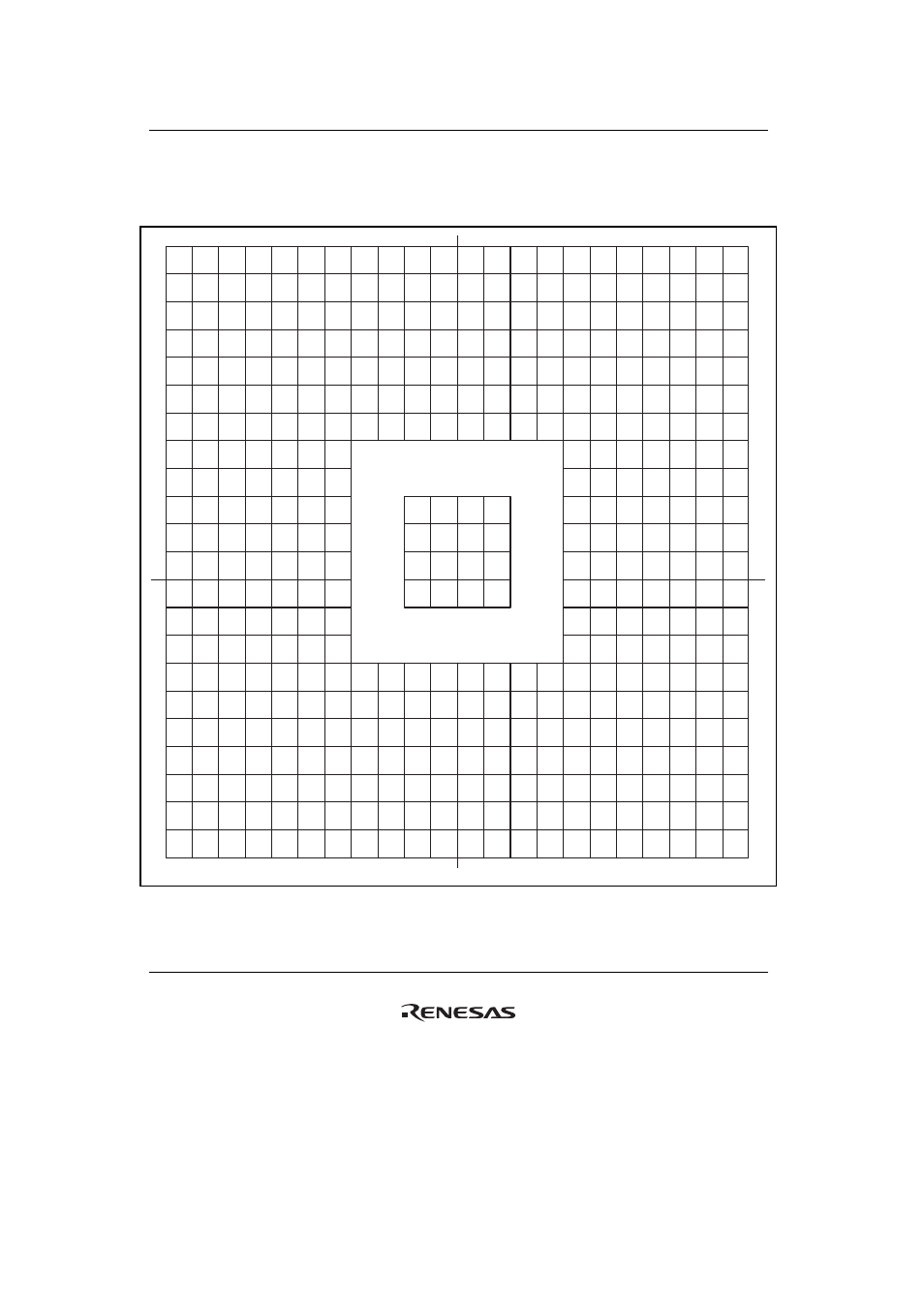

Package: 436-pin FC-BGA, 19 mm x 19 mm, ball pitch: 0.8 mm

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

VSS

MCK1

VSS

MVREF

MA10

MA14

MDQ22

MDQ16

MDQ28

MDQ26

MDM3

VSS

PRESET

SCIF0_SCK

/HSPI_CLK

/

FRE

SCIF1_

SCK

SCIF1_

TXD

SIOF_TXD/

HAC0_SDO

UT/SSI0_

SDATA

SIOF_MCLK

/

HAC_RES

SCIF5_SCK

/HAC1_SD

OUT/SSI1_

SDATA

SCIF5_TXD

/HAC1_

SYNC/

SSI1_WS

A25

VSS

MCK0

VDD-

DDR

MCK1

VDD-

DDR

MCS

VSS

MDQ17

VDD-

DDR

MDQ23

VSS

MDQ31

VSS

VSS

SCIF0_TXD

/HSPI_TX/

FWE

VDDQ

SCIF1_

RXD

VSS

SIOF_SYNC

/HAC0_

SYNC/SSI0_

WS

VDDQ

SCIF5_RXD

/HAC1_

SDIN/SSI1_

SCK

VDDQ

A24

VSS

MCK0

MBKPRST

MBA1

MCAS

MA6

MDQ21

MDQ18

MDQS

2

MDQ25

MDQS

3

MODE0

/

IRL4

/FD4

MODE1

/

IRL5

/FD5

SCIF0_RXD

/HSPI_RX/

FRB

MODE5/

SIOF_MCLK

MODE6/SI

OF_SYNC

SIOF_SCK

/HAC0_BIT

CLK/SSI0_

CLK

HAC1_BI

TCLK/

SSI1_CLK

MODE11

/SCIF4_S

CK/FD3

A23

A22

A21

MCKE

VDD-

DDR

MODT

VSS

MRAS

VDD-

DDR

MA8

VSS

MDQS2

VDD-

DDR

MDQS3

VDDQ

MODE2

/

IRL6

/FD6

SCIF0_CTS

/

INTD/

FCE

VSS

SIOF_RXD

/HAC0_

SDIN/SSI0_

SCK

VDDQ

MODE9/

SCIF4_

TXD/FD1

VSS

A20

VDDQ

A19

MBA0

MA1

MBA2

MA2

MWE

MA0

MA4

MDQ19

MDM2

MDQ27

MDQ29

VDD-

DDR

MODE3

/

IRL7

/FD7

SCIF0_RTS

/

HSPI_CS

/

FSE

MODE8/

SCIF3_

SCK/FD0

MODE10/

SCIF4_RXD

/FD2

CS6

CS5

A18

A17

A16

A15

MA9

VSS

MA11

VDD-

DDR

MA5

VSS

MA12

VDD-

DDR

MDQ20

VSS

MDQ30

MDQ24

VSS

MODE7/

SCIF3_

RXD/FALE

MODE4/

SCIF3_

TXD/FCLE

VDDQ

VSS

A14

VDDQ

A13

VSS

A12

MDQ1

MDQ2

MDQ4

MA13

MA3

MA7

VSS

VDD

VSS

VDD

VSS

VDD

VSS

VDD

VSS

VDD

CS4

A11

A10

A9

A8

A7

MDQ7

VDD-

DDR

MDQ0

VSS

MDQ3

VDD-

DDR

VDD

VSS

VDDQ

A6

VSS

A5

VDDQ

A4

MDQ13

MDQ6

MDQS

0

MDQS0

MDM0

MDQ5

VSS

VDD

R/

W

CS3

A3

A2

A1

A0

MDQ12

VSS

MDQ10

VDD-

DDR

MDQ11

VSS

VDD

VSS

VSS

VSS

VSS

VSS

VSS

CS2

VDDQ

D1

VSS

D0

MDM1

MDQ14

MDQS

1

MDQS1

MDQ15

MDQ8

VSS

VSS

VSS

VSS

VSS

VDD

RD/F

RAME

CS1

CS0

D4

D3

D2

AUDSYNC

AUDAT

A2

AUDAT

A0

AUDAT

A1

VDD-

DDR

MDQ9

VDD

VSS

VSS

VSS

VSS

VSS

D12

D8

WE0/

REG

D7

D6

D5

AUDC

K

VSS

AUDAT

A3

VDDQ

TDO

VSS

VSS

VSS

VSS

VSS

VSS

VDD

VSS

D11

VDDQ

D10

VSS

D9

TCK

TDI

ASEBRK

/BRKACK

THDAG

THDAS

THDCD

VDD

VSS

MODE13

/TCLK/

IOIS16

D16

WE1

D15

D14

D13

VSSQ-

TD

VDDQ

TRST

VSS

TMS

VDDQ

VSS

VDD

VDDQ

BS

VSS

D18

VDDQ

D17

THDCTL

VDDQ-

TD

DACK0

DREQ1

DACK1

DRAK2

/

CE2A

VDD

VSS

VDD

VSS

VDD

VSS

VDD

VSS

VDD

VSS

RDY

BACK/

BSREQ

D22

D21

D20

D19

STATU

S1/DRA

K1

VSS

DREQ0

VDDQ

DREQ2

/

INTB

VSS

IRL3

VDDQ

IRL0

VSS

WE5/

CBE1

DEVSEL/

DCLKOUT

VSS

D52/A

D20

VDDQ

REQ0/

REQOUT

VSS

BREQ/

BSACK

VDDQ

WE2/

IORD

VSS

D23

XTAL

STATUS0/

DRAK0

MPMD

SCIF2_RXD

/SIOF_RXD

DACK2/

SCIF2_TXD/

MMCCMD/

SIOF_TXD

MRESETO

UT/

IRQOUT

IRL1

D35/AD3/

DR3

WE4/

CBE0

D42/AD

10/DG4

D47/AD

15/DB3

STOP

/CDE

PCIFRA

ME/VS

YNC

D51/A

D19

D55/A

D23

D58/A

D26

REQ1

REQ2

D27

D26

D25

D24

EXTAL

VDDQ

NMI

VSS

DACK3/

SCIF2_SCK/

MMCDAT/

SIOF_SCK

VDDQ

IRL2

VSS

D39/AD

7/DG1

VDDQ

D46/AD

14/DB2

LOCK

/ODDF

VDDQ

D50/A

D18

VSS

D57/A

D25

VDDQ

D63/A

D31

VSS

D29

VDDQ

D28

MODE14

VDDQ

-PLL1

VDDA-

PLL1

VDDQ

-PLL2

DREQ3

/

INTC

CLKOU

TENB

MODE12/

DRAK3/

CE2B

D34/AD

2/DR2

D38/AD

6/DG0

D41/AD

9/DG3

D45/AD

13/DB1

PERR

IRDY/

HSYNC

D49/AD

17/DB5

D54/A

D22

D56/A

D24

D60/A

D28

D62/A

D30

GNT0/

GNTIN

GNT2

D31

D30

VSSQ-

PLL1

VDDQ

VDD-

PLL1

VDDQ

VDD-

PLL2

VSS

INTA

VDDQ

D37/AD

5/DR5

VSS

D44/AD

12/DB0

SERR

VSS

D48/AD

16/DB4

VDDQ

WE7/

CBE3

VSS

D61/A

D29

VDDQ

GNT1

VDDQ

WE3/I

OWR

VSS

VSSA-

PLL1

VSS-

PLL1

VSSQ-

PLL2

VSS-

PLL2

CLKO

UT

D32/AD

0/DR0

D33/AD

1/DR1

D36/AD

4/DR4

D40/AD

8/DG2

D43/AD

11/DG5

PAR

TRDY

/DISP

WE6/

CBE2

D53/A

D21

IDSEL

D59/A

D27

PCICLK

/DCLKIN

REQ3

PCIRES

ET

GNT3/

MMCCLK

VSS

PKG TOP VIEW

Figure 1.2 SH7785 Pin Arrangement (Top View)