Renesas SH7781 User Manual

Page 385

11. Local Bus State Controller (LBSC)

Rev.1.00 Jan. 10, 2008 Page 355 of 1658

REJ09B0261-0100

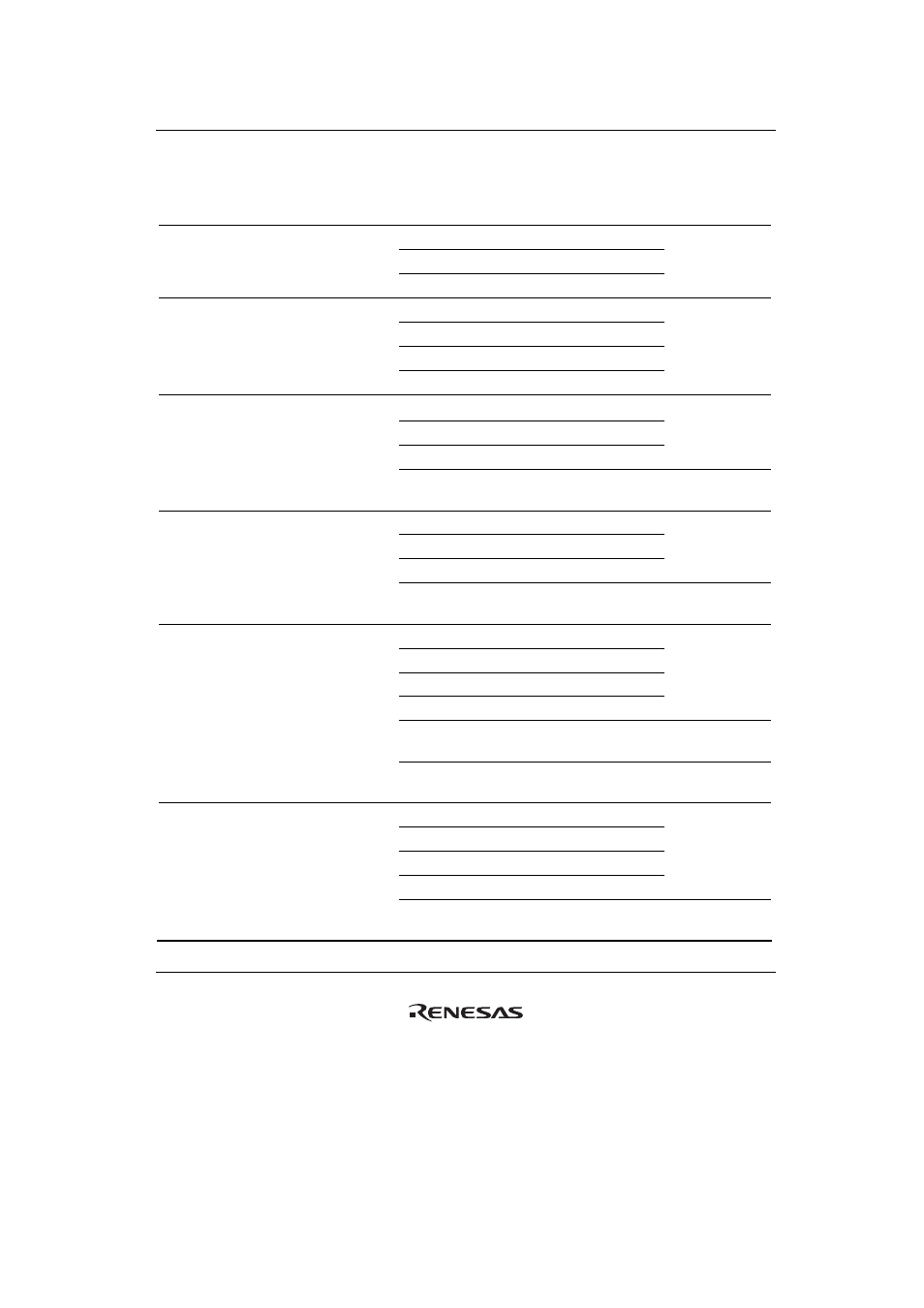

Table 11.2 LBSC External Memory Space Map

Area

External

addresses Size

Connectable

Memory

Specifiable Bus

Width (bits)

Access Size*

7

SRAM

8, 16, 32, 64*

1

Burst ROM

8, 16, 32, 64*

1

0

H'0000 0000 to

H'03FF FFFF

64 Mbytes

MPX 32,

64*

1

8/16/32 bits,

32 bytes

SRAM

8, 16, 32, 64*

2

Burst ROM

8, 16, 32, 64*

2

MPX 32,

64*

2

1

H'0400 0000 to

H'07FF FFFF

64 Mbytes

Byte control SRAM

16, 32, 64*

2

8/16/32 bits,

32 bytes

SRAM

8, 16, 32, 64*

2

Burst ROM

8, 16, 32, 64*

2

MPX 32,

64*

2

8/16/32 bits,

32 bytes

2

H'0800 0000 to

H'0BFF FFFF

64 Mbytes

(DDR2-SDRAM)*

3

16, 32

8/16/32 bits,

32 bytes

SRAM

8, 16, 32, 64*

2

Burst ROM

8, 16, 32, 64*

2

MPX 32,

64*

2

8/16/32 bits,

32 bytes

3 H'0C00

0000

to

H'0FFF FFFF

64 Mbytes

(DDR2-SDRAM)*

3

16, 32

8/16/32 bits,

32 bytes

SRAM

8, 16, 32, 64*

2

Burst ROM

8, 16, 32, 64*

2

MPX 32,

64*

2

Byte control SRAM

16, 32, 64*

2

8/16/32 bits,

32 bytes

(DDR2-SDRAM)*

3

16, 32

8/16/32 bits,

32 bytes

4

H'1000 0000 to

H'13FF FFFF

64 Mbytes

(PCI)*

4

32

8/16/32 bits,

32 bytes

5

64 Mbytes SRAM

8, 16, 32, 64*

2

H'1400 0000 to

H'17FF FFFF

MPX

32,

64*

2

Burst ROM

8, 16, 32, 64*

2

PCMCIA

8,

16*

2, 6

8/16/32 bits,

32 bytes

(DDR2-SDRAM)*

3

16, 32

8/16/32 bits,

32 bytes