Renesas SH7781 User Manual

Page 1579

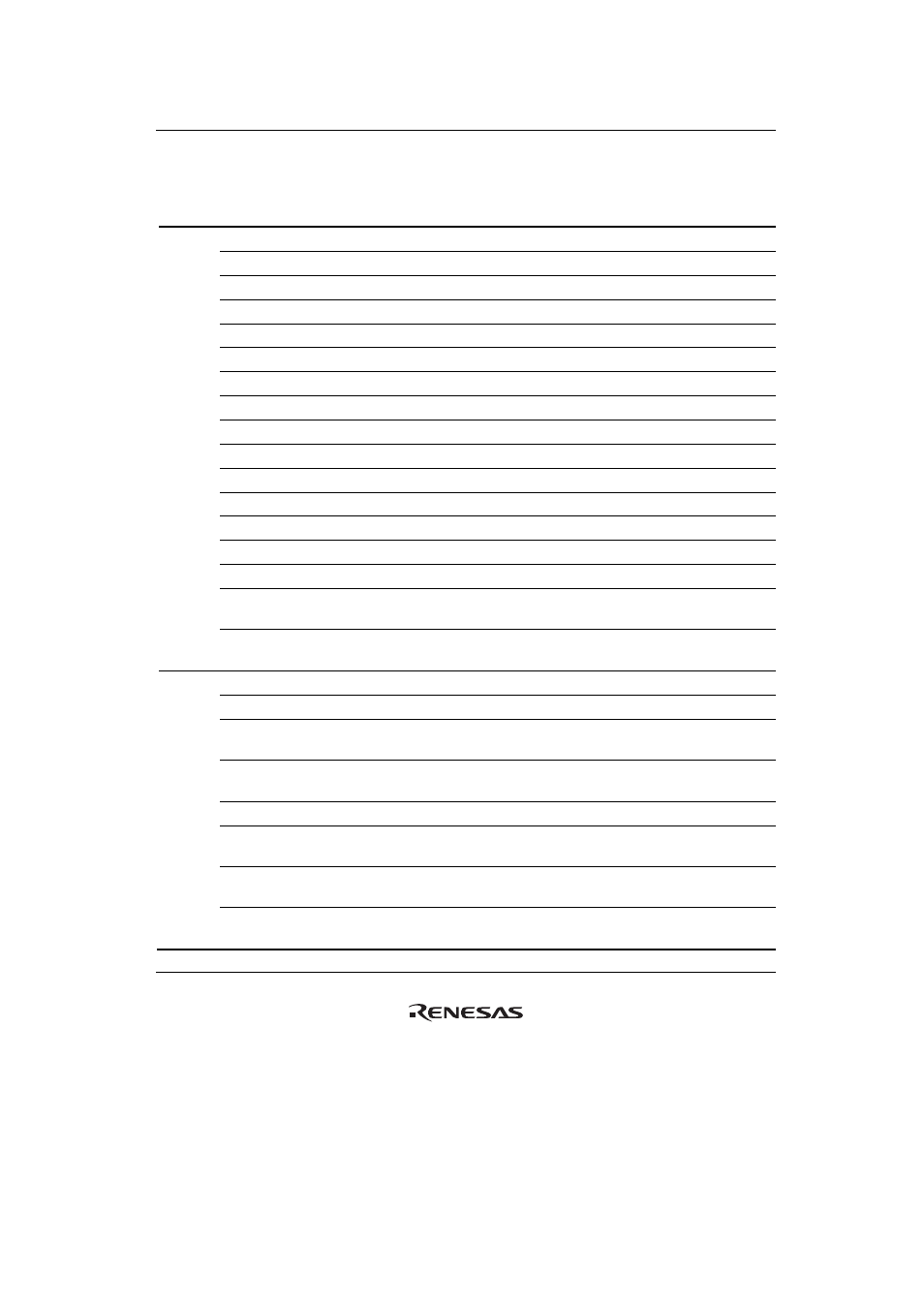

31. Register List

Rev.1.00 Jan. 10, 2008 Page 1549 of 1658

REJ09B0261-0100

Module

Name Name

Abbrev.

Power-on

Reset by

PRESET Pin/

WDT/H-UDI

Manual Reset

by

WDT/Multiple

Exception

Sleep/

Deep Sleep by

SLEEP

Instruction

Module

Standby

DU

Plane 6 transparent color 1 register P6TC1R

Undefined

Retained

Retained

Retained

Plane 6 transparent color 2 register P6TC2R

Undefined

Retained

Retained

Retained

Plane 6 memory length register

P6MLR

H'00000000

Retained

Retained

Retained

Color palette 1 register 000

CP1_000R Undefined

Retained

Retained

Retained

:

:

: : : :

Color palette 1 register 255

CP1_255R Undefined

Retained

Retained

Retained

Color palette 2 register 000

CP2_000R Undefined

Retained

Retained

Retained

:

:

: : : :

Color palette 2 register 255

CP2_255R Undefined

Retained

Retained

Retained

Color palette 3 register 000

CP3_000R Undefined

Retained

Retained

Retained

:

:

: : : :

Color palette 3 register 255

CP3_255R Undefined

Retained

Retained

Retained

Color palette 4 register 000

CP4_000R Undefined

Retained

Retained

Retained

:

:

: : : :

Color palette 4 register 255

CP4_255R Undefined

Retained

Retained

Retained

External synchronization control

register

ESCR H'00000000

Retained Retained Retained

Output signal timing adjustment

register

OTAR H'00000000

Retained Retained Retained

GDTA

GA mask register

GACMR

H'0000 0000

H'0000 0000

Retained

Retained

GA enable register

GACER

H'0000 0000

H'0000 0000

Retained

Retained

GA processing end interrupt source

indicating register

GACISR

H'0000 0000

H'0000 0000

Retained

Retained

GA processing end interrupt source

indication clear register

GACICR

H'0000 0000

H'0000 0000

Retained

Retained

GA interrupt enable register

GACIER

H'0000 0000

H'0000 0000

Retained

Retained

GA CL input data alignment

register

DRCL_CTL H'0000 0000

H'0000 0000

Retained

Retained

GA CL output data alignment

register

DWCL_CTL H'0000 0000

H'0000 0000

Retained

Retained

GA MC input data alignment

register

DRMC_CTL H'0000 0000

H'0000 0000

Retained

Retained