Renesas SH7781 User Manual

Page 332

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 302 of 1658

REJ09B0261-0100

(2)

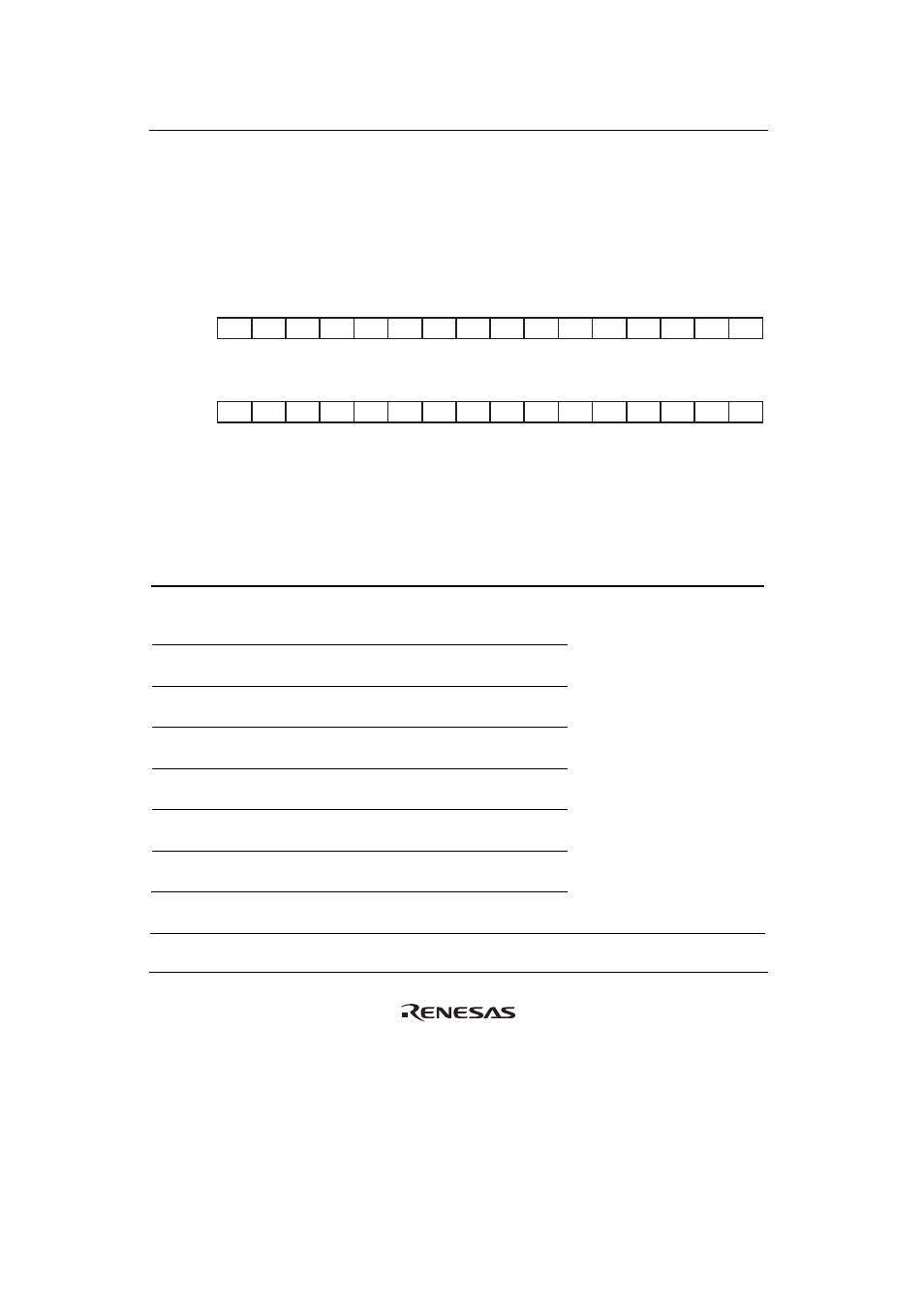

Interrupt Source Register (Not affected by Mask Setting) (INT2A0)

INT2A0 is a 32-bit read-only register that indicates the interrupt sources of on-chip peripheral

modules. Even if an interrupt is masked by the interrupt mask register, the corresponding bit in

INT2A0 is set (further interrupt operation is not performed for the corresponding bit). Use

INT2A1 instead if the bits for the interrupt sources masked by the interrupt mask registers should

not be set.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

—

—

—

—

—

—

—

—

—

—

—

—

—

0

0

0

—

—

—

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Table 10.6 shows the correspondence between bits in INT2A0 and the interrupt sources.

Table 10.6 Correspondence between Bits in INT2A0 and Interrupt Sources

Bit

Initial

Value R/W

Source

Function

Description

31 to

29

All 0

R

Reserved

These bits are always read

as 0. The write value

should always be 0.

28

Undefined R

GDTA

GDTA interrupt source

indication

27

Undefined R

DU

DU interrupt source

indication

26 Undefined

R SSI

channel 1

SSI channel 1 interrupt

source indication

25 Undefined

R SSI

channel 0

SSI channel 0 interrupt

source indication

24

Undefined R

GPIO

GPIO interrupt source

indication

23

Undefined R

FLCTL

FLCTL interrupt source

indication

These bits indicate the

interrupt source of each

peripheral module that is

generating an interrupt.

(INT2A0 is not affected by the

setting of the interrupt mask

register).

0: No interrupt

1: An interrupt has occurred

Note: Interrupt sources can

also be identified by

directly reading the

INTEVT code. In this

case, reading from this

register is not required.

22

Undefined R

MMCIF

MMCIF interrupt source

indication