Renesas SH7781 User Manual

Page 1670

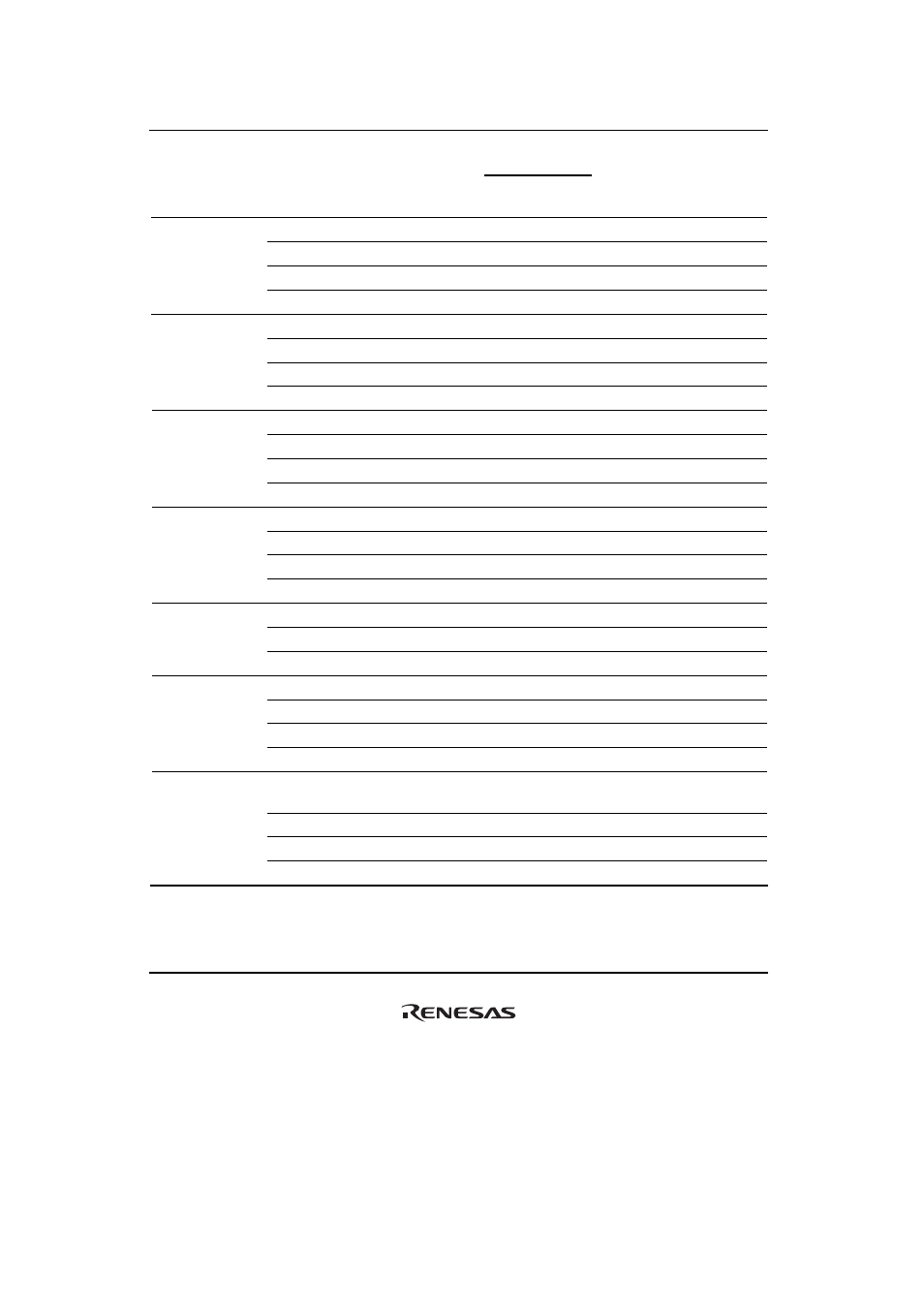

Appendix

Rev.1.00 Jan. 10, 2008 Page 1640 of 1658

REJ09B0261-0100

Reset

Pin Name

(LSI level)

Pin Name

(Module level)

Related

Module I/O

Power

-on Manual Sleep

Module

Standby

Bus

Release

Port J5 (default) GPIO

I/O

PI

K

K

⎯

K

SIOF_RXD SIOF

I

⎯

I I I I

SIOF_RXD/

HAC0_SDIN/

SSI0_SCK

HAC0_SDIN HAC I

⎯

I I I I

SSI0_SCK

SSI

I/O

⎯

K K K K

Port J2 (default) GPIO

I/O

PI

K

K

⎯

K

SIOF_SCK SIOF

I/O

⎯

L K

K K

HAC0_BITCLK HAC

I

⎯

I I I I

SIOF_SCK/

HAC0_BITCLK/

SSI0_CLK

SSI0_CLK SSI I

⎯

I I I I

Port J4 (default) GPIO

I/O

PI

K

K

⎯

K

SIOF_SYNC SIOF I/O

⎯

L K

K K

HAC0_SYNC HAC O

⎯

O O O O

SIOF_SYNC/

HAC0_SYNC/

SSI0_WS

SSI0_WS SSI

I/O

⎯

I K

K K

Port J6 (default) GPIO

I/O

PI

K

K

⎯

K

SIOF_TXD SIOF

O

⎯

H K K K

HAC0_SDOUT HAC

O

⎯

O O O O

SIOF_TXD/

HAC0_SDOUT/

SSI0_SDATA

SSI0_SDATA SSI

I/O

⎯

I K

K K

Port J1 (default) GPIO

I/O

PI

K

K

⎯

K

HAC1_BITCLK HAC

I

⎯

I I I I

HAC1_BITCLK/

SSI1_CLK

SSI1_CLK SSI I

⎯

I I I I

Port J7 (default) GPIO

I/O

PI

K

K

⎯

K

SCIF5_TXD SCIF O

⎯

Z O

O O

HAC1_SYNC HAC O

⎯

O O O O

SCIF5_TXD/

HAC1_SYNC/

SSI1_WS

SSI1_WS SSI

I/O

⎯

I K

K K

Port N7

(default)

GPIO I/O

PI K

K

⎯

K

SCIF5_RXD SCIF I

⎯

I I I I

SCIF5_RXD/

HAC1_SDIN/

SSI1_SCK

HAC1_SDIN HAC I

⎯

I I I I

SSI1_SCK

SSI

I/O

⎯

I K

K K