5 gpio interrupt set register (int2gpic) – Renesas SH7781 User Manual

Page 352

10. Interrupt Controller (INTC)

Rev.1.00 Jan. 10, 2008 Page 322 of 1658

REJ09B0261-0100

10.3.5

GPIO Interrupt Set Register (INT2GPIC)

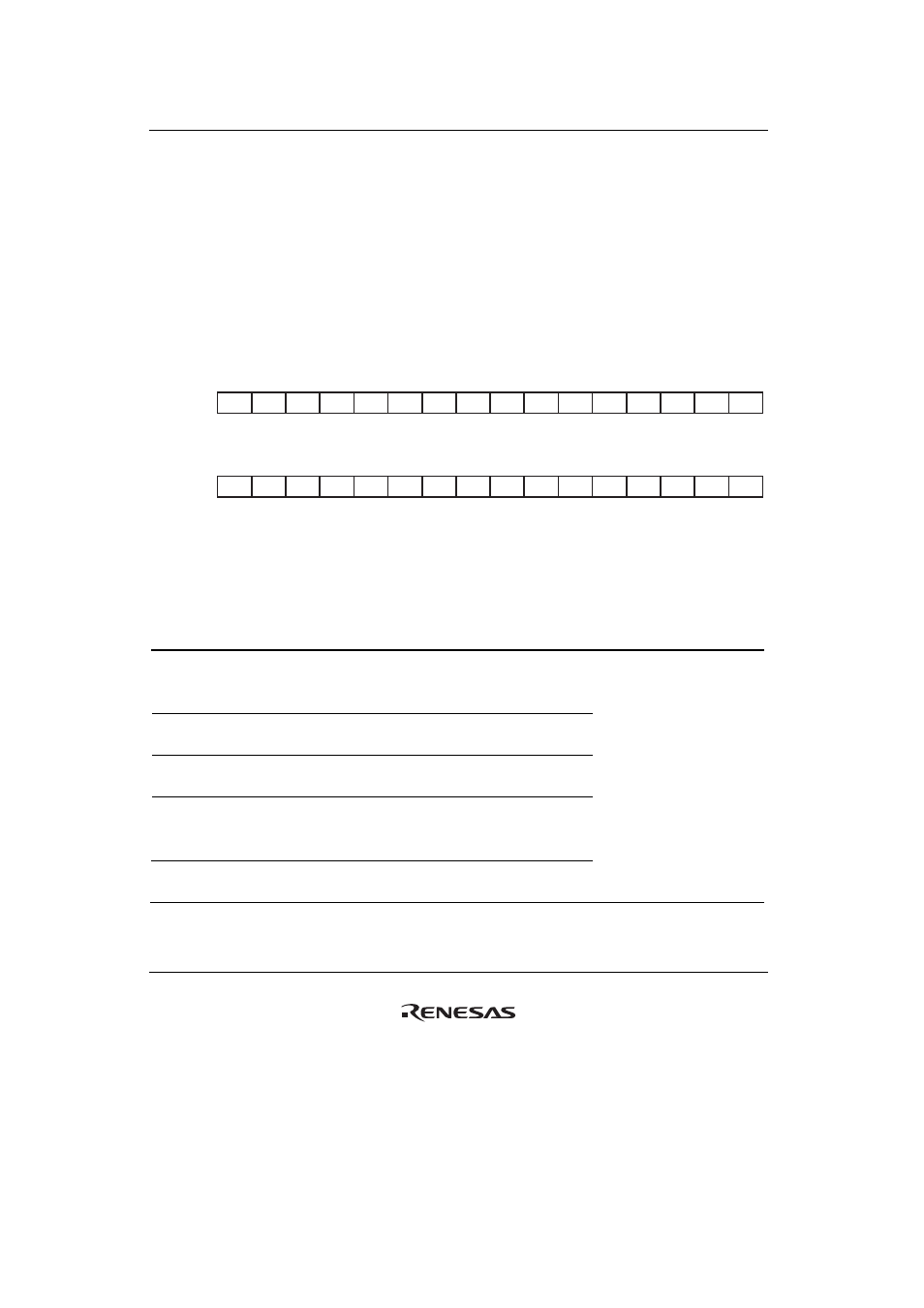

INT2GPIC enables interrupt requests input from the pins 0 to 5 of port E, pins 1 to 4 of port H,

pins 6 and 7 of port L, as GPIO interrupts.

A GPIO interrupt is a low-active interrupt. Enable interrupt requests after setting the pins

corresponding to the port control register (E, H, and L) used for GPIO interrupts to be input pins

from ports For the port control registers, see section 28, General Purpose I/O Ports (GPIO).

The timing required to reflect the register value is guaranteed by writing to this register, and then,

reading from this register once (the interrupt request is reflected).

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R/W

R

R

R

R

R/W

R/W

R

R

R

R

R

R

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R

R

R

R

R

R/W

R/W

R/W

R

R

R

R

R

Bit:

Initial value:

R/W:

Table 10.11 shows the correspondence between bits in INT2GPIC and the functions.

Table 10.11 Correspondence between Bits in INT2GPIC and GPIO Interrupts

Bit Name

Initial

Value R/W Function

Description

31 to

26

⎯ All

0

R/W

Reserved

These bits are always read as 0.

The write value should always be 0.

25

PORTL7E 0

R/W

Enables interrupt request from pin 7

of port L.

24

PORTL6E 0

R/W

Enables interrupt request from pin 6

of port L.

23 to

20

⎯ All

0

R/W

Reserved

These bits are always read as 0.

The write value should always be 0.

Enables GPIO interrupt

request for each pin.

0: Disable the

corresponding interrupt

request

1: Enable the

corresponding interrupt

request

19

PORTH4E 0

R/W

Enables interrupt request from pin 4

of port H.