6 sdram timing register 1 (dbtr1) – Renesas SH7781 User Manual

Page 522

12. DDR2-SDRAM Interface (DBSC2)

Rev.1.00 Jan. 10, 2008 Page 492 of 1658

REJ09B0261-0100

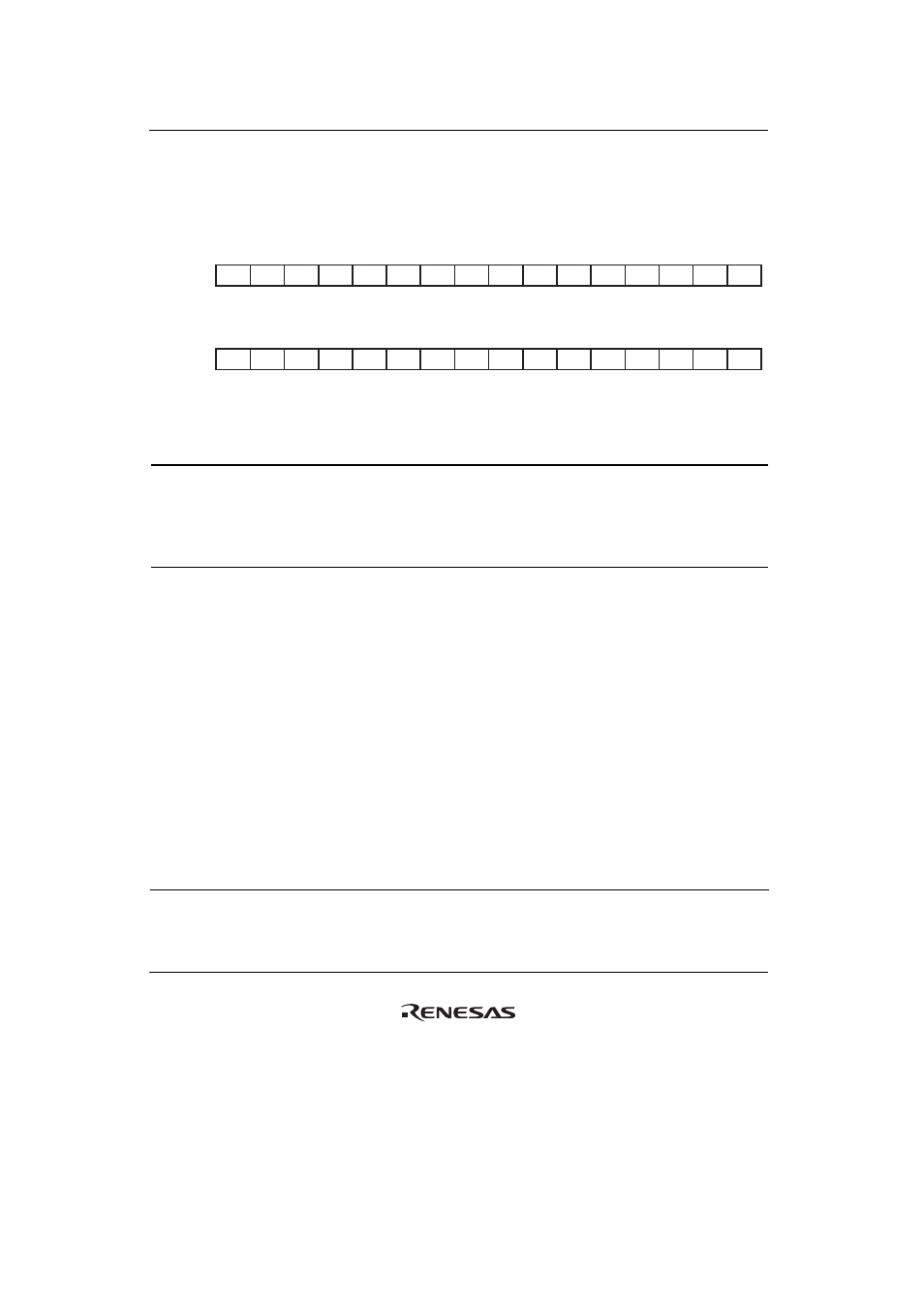

12.4.6

SDRAM Timing Register 1 (DBTR1)

The SDRAM timing register 1 (DBTR1) is a readable/writable register. It is initialized only upon

power-on reset.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

TRP0

TRP1

TRP2

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R

R

R

R

R

R

R

R

R

R

R

R

R

BIt:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

TWR0

TWR1

TWR2

⎯

⎯

⎯

⎯

⎯

TRRD0

TRRD1

TRRD2

⎯

⎯

⎯

⎯

⎯

R/W

R/W

R/W

R

R

R

R

R

R/W

R/W

R/W

R

R

R

R

R

BIt:

Initial value:

R/W:

Bit Bit

Name

Initial

Value R/W

Description

31 to 19

⎯

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

Operation when a value other than 0 is written is not

guaranteed.

18 to 16 TRP2 to

TRP0

001

R/W

tRP (PRE-ACT/REF period) Setting Bits

These bits set the PRE-ACT minimum period constraint

for the same bank. These bits should be set according

to the DDR2-SDRAM specifications. The number of

cycles is the number of DDR clock cycles.

000: Setting prohibit (If specified, correct operation

cannot be guaranteed.)

001: 2 cycles

010: 3 cycles

011: 4 cycles

100: 5 cycles

101: Setting prohibit (If specified, correct operation

cannot be guaranteed.)

:

111: Setting prohibit (If specified, correct operation

cannot be guaranteed.)