Renesas SH7781 User Manual

Page 642

13. PCI Controller (PCIC)

Rev.1.00 Jan. 10, 2008 Page 612 of 1658

REJ09B0261-0100

(13)

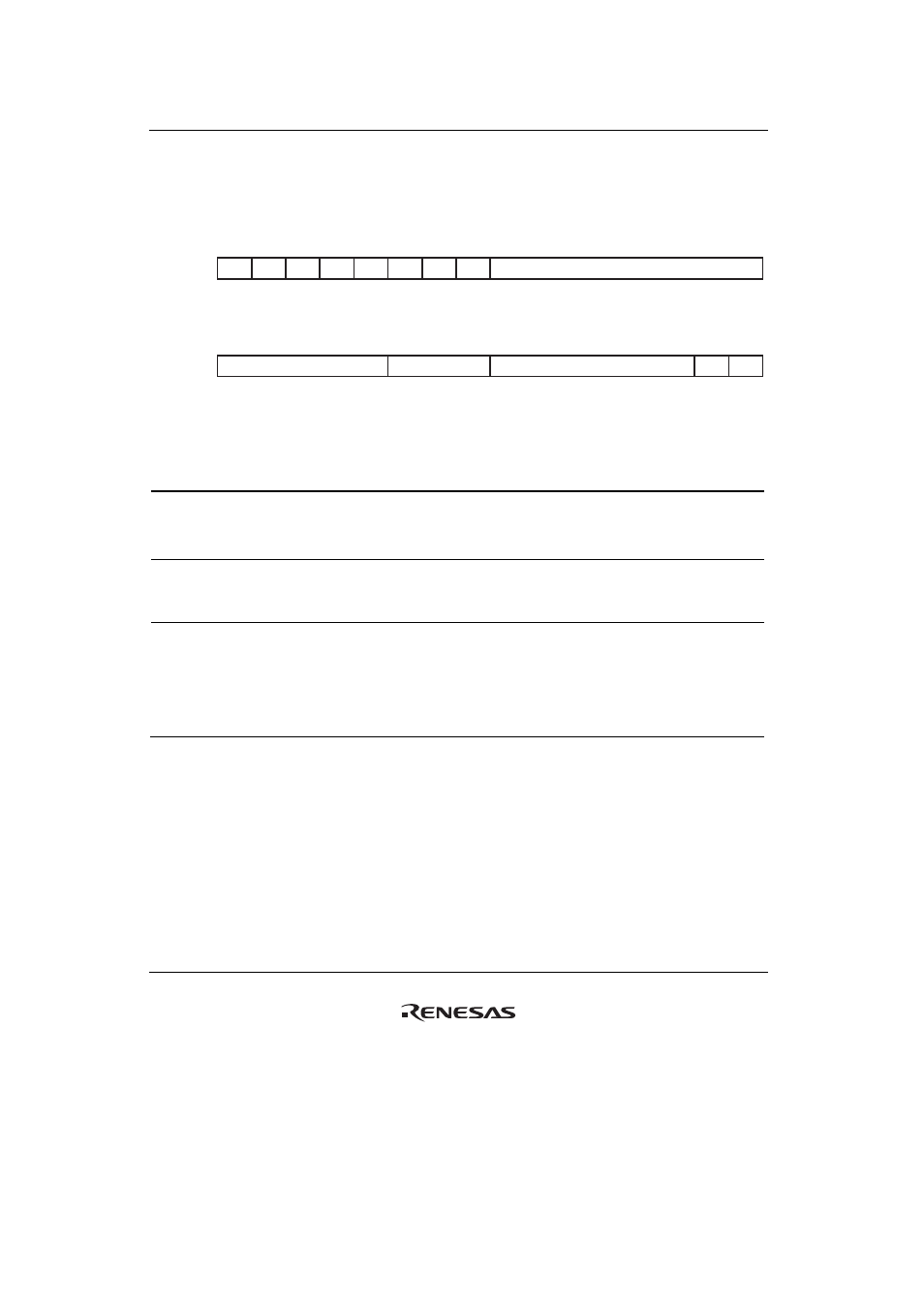

PCI PIO Address Register (PCIPAR)

Setting this register generates configuration cycles on the PCI bus. For details, see section 13.4.5

(2), Configuration Space Access.

SH R/W:

PCI R/W:

SH R/W:

PCI R/W:

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

Bit:

Initial value:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

x

x

x

x

x

x

x

x

—

—

—

—

—

—

—

—

0

0

0

0

0

0

1

0

BN

—

—

—

—

—

—

CCIE

—

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

x

x

x

x

x

x

x

x

x

x

x

x

x

x

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

CRA

FN

DN

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

Bit:

Initial value:

Bit Bit

Name

Initial

Value R/W Description

31 CCIE 1

SH:

R

PCI:

⎯

Configuration Cycle Issue Enable

0: Indicates that configuration cycle issue is disable

1:

⎯

30 to 24

⎯

All 0

SH: R

PCI:

⎯

Reserved

These bits are always read as 0. The write value

should always be 0.

23 to 16 BN

H'xx

SH: R/W

PCI:

⎯

PCI Bus Number

These bits specify a PCI bus number for the

configuration access target. The bus number 0

indicates the bus to which the PCIC is connected. A

bus number is represented by an 8-bit value in the

range from 0 to 255.