2 watchdog timer control/status register (wdtcsr) – Renesas SH7781 User Manual

Page 794

16. Watchdog Timer and Reset (WDT)

Rev.1.00 Jan. 10, 2008 Page 764 of 1658

REJ09B0261-0100

16.3.2

Watchdog Timer Control/Status Register (WDTCSR)

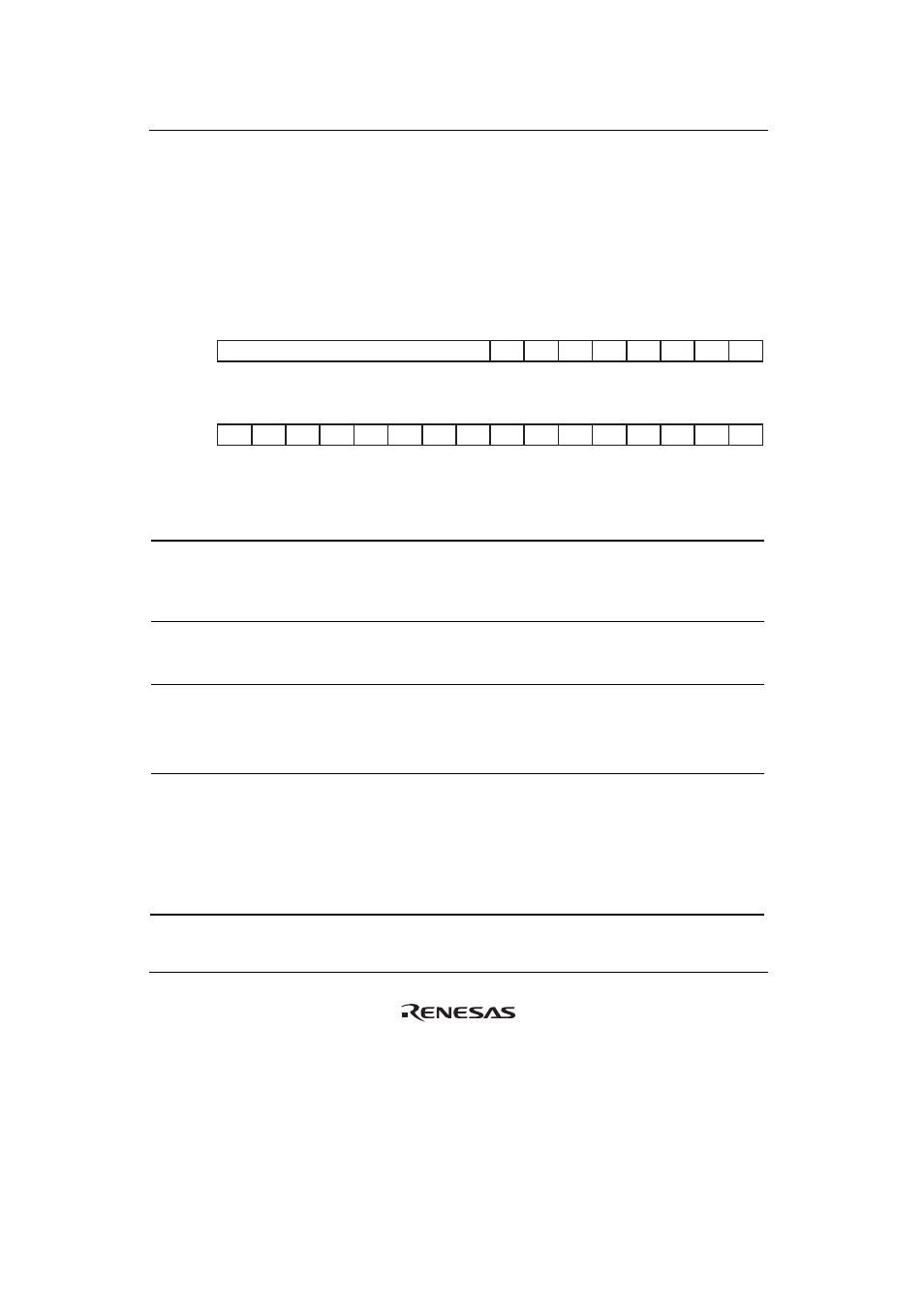

WDTCSR is a 32-bit readable/writable register comprising timer mode-selecting bits and overflow

flags.

WDTCSR should be written to as a longword unit, with H'A5 in the most significant byte. The

value read from this byte is always H'00. WDTCSR is only rest by a power-on reset caused by the

PRESET pin.

16

17

18

19

20

21

22

23

24

25

26

27

28

29

31

30

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

Initial value:

R/W:

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

14

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

⎯

⎯

⎯

IOVF

WOVF

RSTS

WT/

IT

TME

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

R

R

R

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R

R

R

R

Bit:

Initial value:

R/W:

Code for writing (H'A5)

Bit Bit

Name

Initial

Value R/W Description

31 to 24 (Code for

writing)

All 0

R/W

Code for writing (H'A5)

These bits are always read as H'00. When writing to

this register, the value written to these bits must be

H'A5.

23 to 8

⎯ All

0

R

Reserved

These bits are always read as 0. The write value

should always be 0.

7 TME

0 R/W

Timer

Enable

Starts or stops the timer operation.

0: Stops counting up.

1: Starts counting up.

6 WT/

IT

0

R/W

Timer Mode Select

Specifies whether the WDT is used as a watchdog

timer or interval timer. Up counting may not be

performed correctly if this bit is modified while the

WDT is running.

0: Interval timer mode

1: Watchdog timer mode